# **MULTI-TIME ANALYSIS OF CMOS CIRCUITS**

by

Chien-Ting (Justin) Chen

A Thesis

Presented to Lakehead University

In Partial Fulfillment of the Requirement for the Degree of

Master of Applied Science

in

Control Engineering

Thunder Bay, Ontario, Canada

April 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada

Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1Ă 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-42153-6 Our file Notre référence ISBN: 978-0-494-42153-6

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses commercial purposes, in microform, paper, electronic and/or any other formats.

worldwide, for commercial or non-

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres. sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **Abstract**

Transient simulation of circuits with widely separated time constants and fast periodic excitations is not efficient because a long simulation period with small time steps is required. One approach to simulate the transient behaviour more efficiently is known as the Multi Partial Differential Equation (MPDE). In the MPDE the system ordinary differential equations that describe a circuit is transformed into a system of partial differential equations with two time variables, one for the fast periodic variations and another for the slow transient evolution. This method has been implemented in a general-purpose circuit simulator program named Carrot. This thesis presents progress towards the development that simulator. The main contributions of this thesis are the implementation and validation of MOSFET models in the simulator and the study of the performance of the MPDE approach (as currently implemented in Carrot) applied to complex CMOS circuits. An overview of concepts relevant for this work is presented, followed by a detailed description of the MOSFET model implementation. Next, the design of an integrated CMOS ring voltage-controlled oscillator is presented. This is followed by simulation case studies. The simulation results indicate that the MPDE approach can achieve orders of magnitude of improvement in simulation speed compared to regular transient analysis. This thesis concludes with recommendations for future research.

## Acknowledgements

I would like to thank my supervisor Dr. Carlos E. Christoffersen for making grad school a rewarding experience. Due to his easy going personality, it was fun to work with him and the advice and supports he gave are always greatly appreciated.

Thanks to Canadian Microelectronics Corporation (CMC) for providing the software and Taiwan Semiconductor Manufacturing Corporation (TSMC) as well for fabricating the ICs (Integrated Circuits). Thanks to James Dietrich who helped us mounting the package on top of a test fixture and also modifying the test fixture board.

Thanks to all classmates I met in grad study. Without their supports, I will not be able to finish my work alone. Special thanks to Jerry Dou and WeiBo Li who have helped me, given advice, and supported along the way.

I would like to take this opportunity to thank my parents who have supported my education and living expenses for the last couple years. Their support and encouragement mean more to me than I can properly convey. Without their support and love, I will never be able to hold this master degree.

# **Contents**

| CHAP | TER 1                                   | INTRODUCTION                                                  | 1  |

|------|-----------------------------------------|---------------------------------------------------------------|----|

| 1.1  | Мот                                     | IVATION                                                       | 1  |

| 1.2  | Ove                                     | RVIEW                                                         | 2  |

| ~**  |                                         |                                                               | _  |

| СНАР |                                         | LITERATURE REVIEW                                             |    |

| 2.1  | Intr                                    | ODUCTION                                                      | 3  |

| 2.2  | MOS                                     | SFET MODELING                                                 | 4  |

| 2.3  | Mul                                     | ti-Time Simulation Methods                                    | 5  |

| 2    | 2.3.1                                   | MPDE                                                          | 6  |

|      | .3.2                                    | WaMPDE                                                        |    |

| 2.4  | .3.3<br>Com                             | EHB                                                           |    |

|      | • • • • • • • • • • • • • • • • • • • • | PANION MODELS                                                 |    |

| _    | .4.1                                    | Linear Transconductances Linear Capacitors                    |    |

|      | .4.2                                    | Non-linear Current Sources                                    |    |

|      | .4.4                                    | Non-linear Capacitances                                       |    |

| 2.5  |                                         | CT-ORIENTED CIRCUIT SIMULATORS                                |    |

| 2.6  |                                         | RENCE CIRCUIT SIMULATORS                                      |    |

|      |                                         |                                                               |    |

| CHAP |                                         | MOSFET MODEL IMPLEMENTATION AND TESTING                       |    |

| 3.1  | Intro                                   | ODUCTION                                                      | 20 |

| 3.2  | Circ                                    | UIT SIMULATION PROGRAM ARCHITECTURE                           | 21 |

| 3.3  | DCC                                     | COMPONENT IMPLEMENTATION                                      | 23 |

| 3.   | .3.1                                    | Diode Model                                                   | 26 |

| 3.   | .3.2                                    | Threshold Voltage                                             |    |

| 3.   | .3.3                                    | Subthreshold Voltage and Saturation Voltage                   | 33 |

| _    | .3.4                                    | Drain-to-Source Current                                       |    |

|      | .3.5                                    | Parasitic Resistors                                           |    |

| 3.4  |                                         | OMPONENT IMPLEMENTATION                                       |    |

| 3.5  | Mod                                     | el Verification                                               | 47 |

| CHAP | TER 4                                   | DESIGN OF A RING VCO                                          | 55 |

| 4.1  | Intro                                   | DDUCTION                                                      | 55 |

| 4.2  | Voli                                    | AGE-CONTROLLED OSCILLATOR (VCO) PRINCIPLES AND DESIGN ASPECTS | 56 |

| 4.   | .2.1                                    | Ring VCO                                                      | 57 |

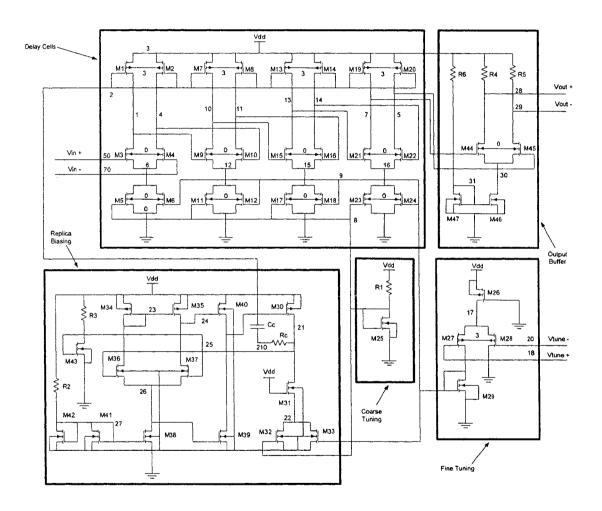

| 4.3  | RING                                    | VCO SCHEMATIC DESIGN                                          |    |

| 4.   | 3.1                                     | Differential Delay Circuit Design                             | 64 |

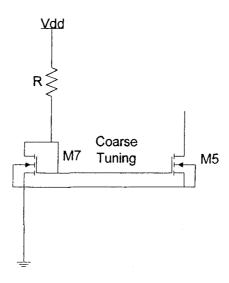

| 4.   | 3.2                                     | Coarse Tuning Circuit Design                                  | 69 |

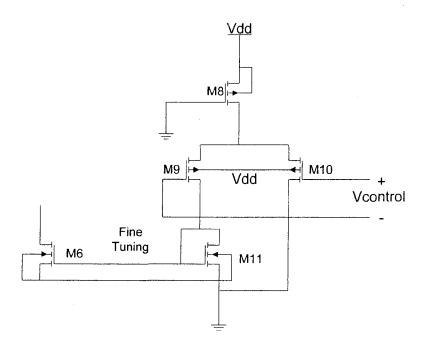

|      | 3.3                                     | Fine Tuning Circuit Design                                    |    |

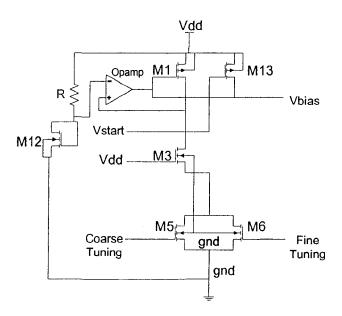

|      | 3.4                                     | Replica Biasing Circuit Design  Output Buffer Circuit Design  |    |

|      | 3.5                                     |                                                               | 77 |

| 4.5  | SIMULATION RESULTS                                                                                                                                   | 91              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| СНАР | TER 5 MULTI-TIME ANALYSIS / ENVELOPE HARMONIC BALANCE                                                                                                | 94              |

| 5.1  | Introduction                                                                                                                                         | 94              |

| 5.2  | Companion Models for EHB Analysis                                                                                                                    | 94              |

| 5    | 5.2.1 Linear Transconductances 5.2.2 Linear Capacitor 5.2.3 Nonlinear Current Sources 6.2.4 Nonlinear Capacitors RING OSCILLATOR WITH OPEN LOOP TEST | 95<br>98<br>100 |

| 5.4  | SIMULATION RESULTS                                                                                                                                   | 110             |

| СНАР | TER 6 CONCLUSION AND FUTURE WORK                                                                                                                     | 115             |

| 6.1  | Conclusion                                                                                                                                           | 115             |

| 6.2  | FUTURE WORK                                                                                                                                          | 116             |

| APPE | NDIX A                                                                                                                                               | 118             |

| Ехр  | ERIMENTAL RESULTS                                                                                                                                    | 118             |

| APPE | NDIX B                                                                                                                                               | 121             |

| REFE | RENCE                                                                                                                                                | 127             |

# **List of Figures**

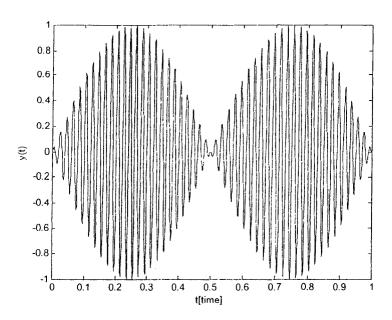

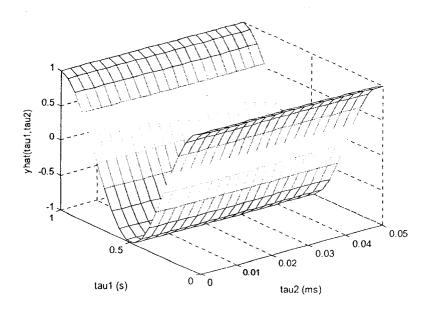

| Figure 2.1 Example of two-tone quasi-periodic signal y(t)                    | 7    |

|------------------------------------------------------------------------------|------|

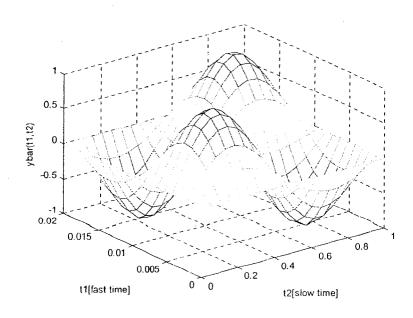

| Figure 2.2 Example of two-periodic bivariate waveform                        | 7    |

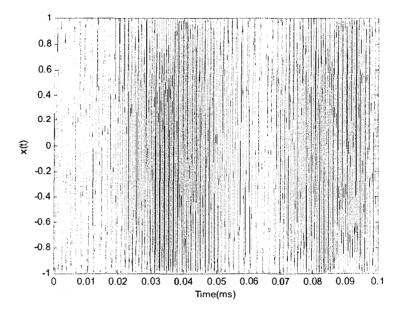

| Figure 2.3 Example of the FM signal                                          | 9    |

| Figure 2.4 Example of the FM signal using MPDE method.                       | 10   |

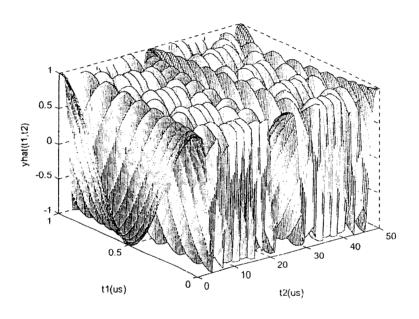

| Figure 2.5 Example of the FM signal using WaMPDE method                      | 11   |

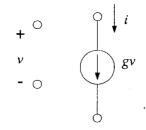

| Figure 2.6 Companion model of a linear transconductance                      |      |

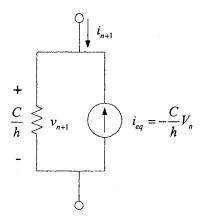

| Figure 2.7 Companion model of a linear capacitor                             |      |

| Figure 2.8 Non-linear current source                                         | 15   |

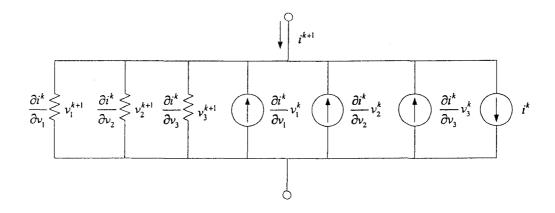

| Figure 2.9 Companion model of a nonlinear current source                     | 16   |

| Figure 2.10 Companion model for a nonlinear capacitance                      | 17   |

| Figure 3.1 UML class diagram of OP class                                     |      |

| Figure 3.2 Typical enhancement-mode MOS structure                            | 24   |

| Figure 3.3 Intrinsic model of an n-Channel MOSFET                            | 24   |

| Figure 3.4 Nonlinear voltage controlled current source template              | 38   |

| Figure 3.5 Linear voltage controlled current source template                 |      |

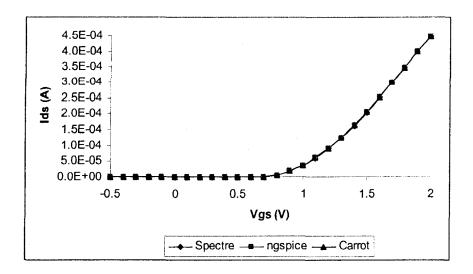

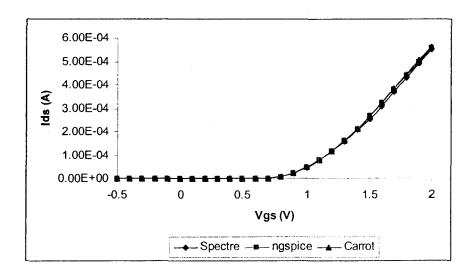

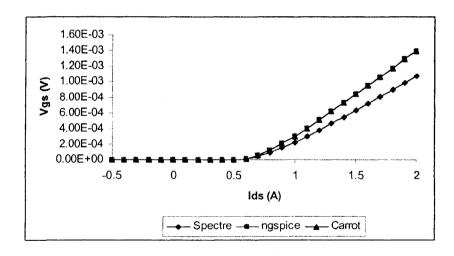

| Figure 3.6 Vgs vs Ids at Vmax=1e5 and (W/L=30u/3u)                           | 48   |

| Figure 3.7 Vgs vs Ids at Vmax=0 and (W/L=30u/3u)                             | . 48 |

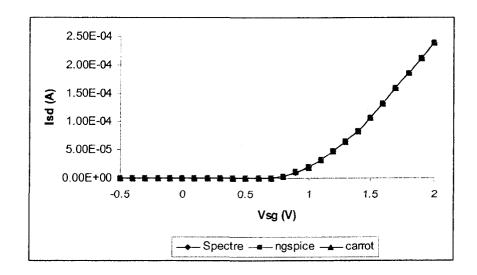

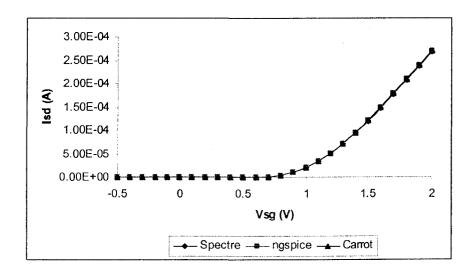

| Figure 3.8 Vsg vs Isd at Vmax=1e5 and (W/L=30u/3u)                           | 49   |

| Figure 3.9 Vsg vs Isd at Vmax=0 and (W/L=30u/3u)                             | . 49 |

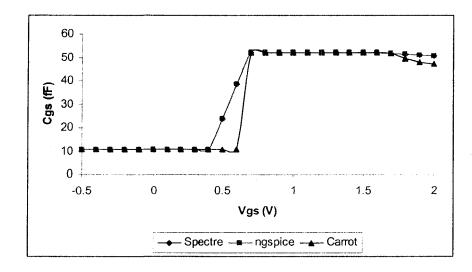

| Figure 3.10 Cgs vs Vgs for NMOSFET at Vmax=1e5 and (W/L=30u/3u)              | . 51 |

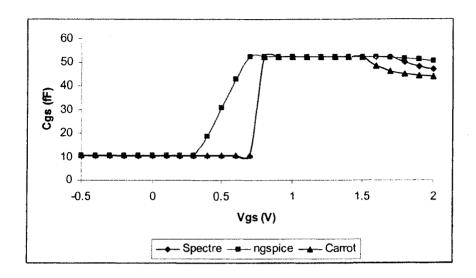

| Figure 3.11 Cgs vs Vgs for PMOSFET at Vmax=1e5 and (W/L=30u/3u)              | . 52 |

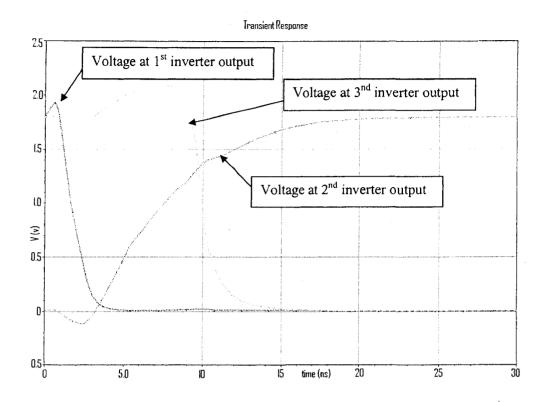

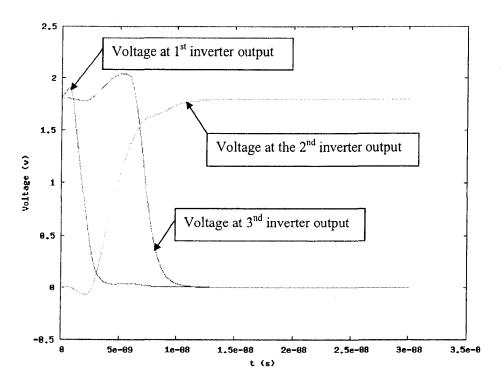

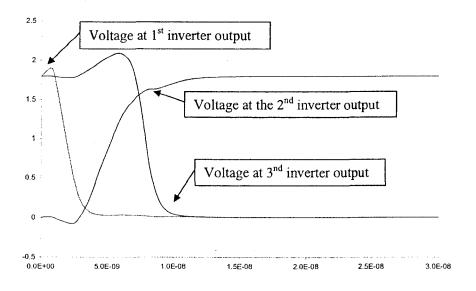

| Figure 3.12 Three stage inverter transient simulation using Spectre          |      |

| Figure 3.13 Three stage inverter transient simulation using Carrot           |      |

| Figure 3.14 Three stage inverter transient simulation using ngspice          | . 54 |

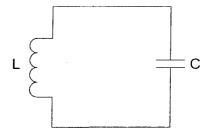

| Figure 4.1 Ideal LC tank                                                     |      |

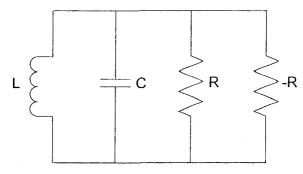

| Figure 4.2 Practical LC tank with negative resistance                        | 57   |

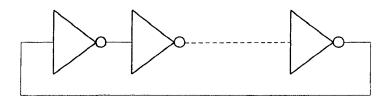

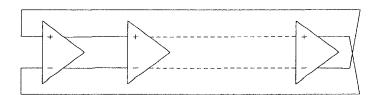

| Figure 4.3 Single-ended ring oscillator block diagram                        | . 58 |

| Figure 4.4 Single-ended ring VCO schematic                                   | 59   |

| Figure 4.5 Differential ring oscillator block diagram                        | . 59 |

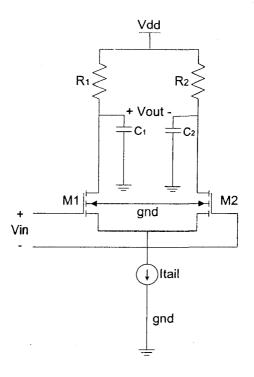

| Figure 4.6 Simplified differential delay cell circuit schematic              | . 60 |

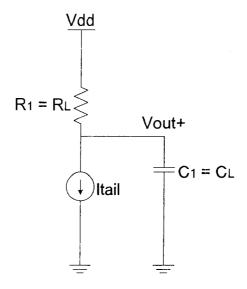

| Figure 4.7 Left-hand side of the source-coupled pair differential delay cell | . 61 |

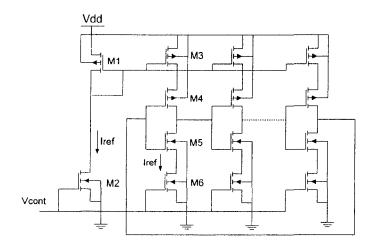

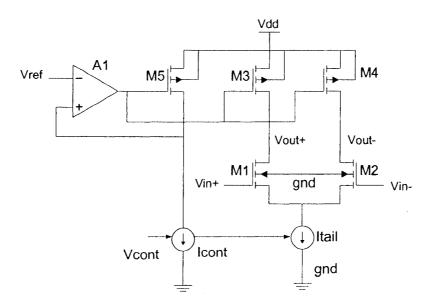

| Figure 4.8 VCO with replica biasing circuit schematic                        | . 62 |

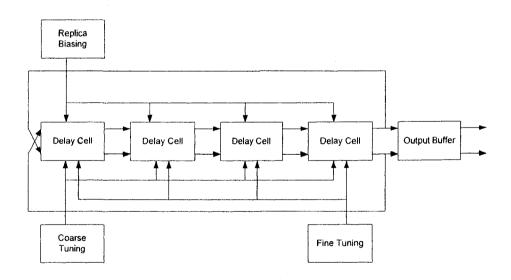

| Figure 4.9 Differential ring VCO block diagram                               | . 63 |

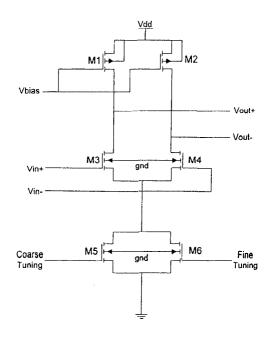

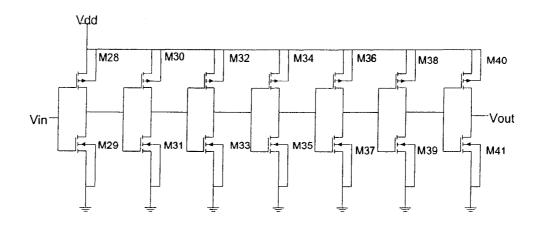

| Figure 4.10 Basic differential delay cell schematic                          | . 65 |

| Figure 4.11 Pre-layout simulation of delay cells                             | . 67 |

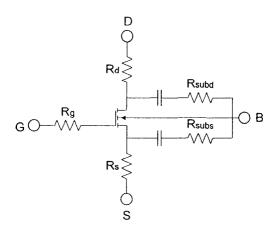

| Figure 4.12 A MOSFET RF model based on BSIM3v3                               | . 68 |

| Figure 4.13 Coarse tuning cell schematic                                     | . 69 |

| Figure 4.14 Fine tuning cell schematic                                       | . 71 |

| Figure 4.15 Replica biasing cell schematic                                   |      |

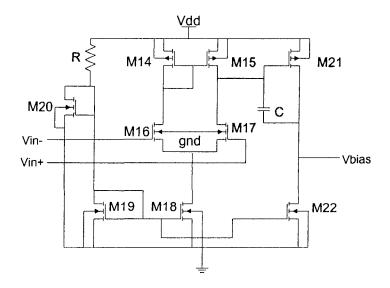

| Figure 4.16 Operational amplifier cell schematic                             |      |

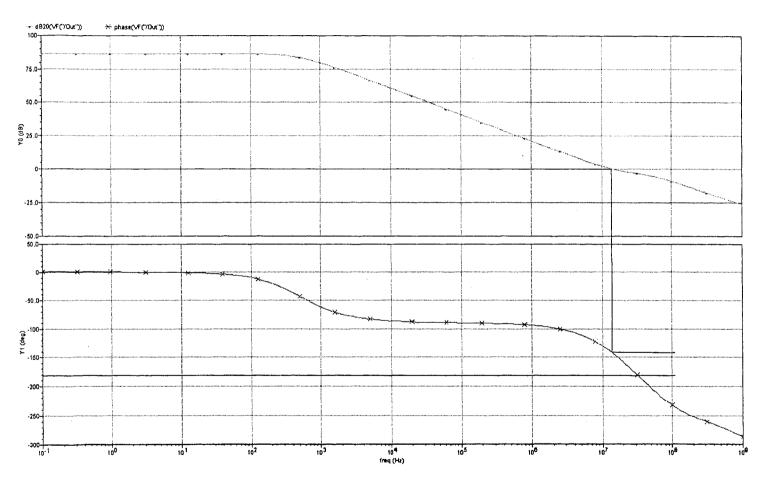

| Figure 4.17 The open-loop frequency response of the op-amp                   | . 76 |

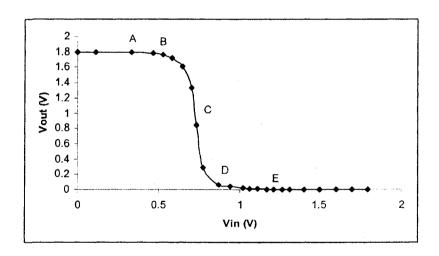

| Figure 4.18 Operating regions of the nMOS and the pMOS transistors                | 77    |

|-----------------------------------------------------------------------------------|-------|

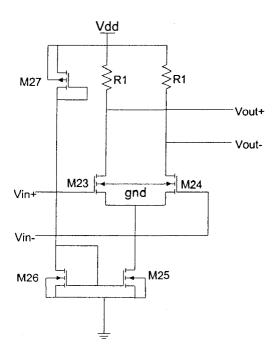

| Figure 4.19 The 1st stage differential output buffer cell schematic               | 78    |

| Figure 4.20 Pre-layout simulation at the 1st buffer output                        | 79    |

| Figure 4.21 The 2 <sup>nd</sup> stage output buffer cell schematic                | 80    |

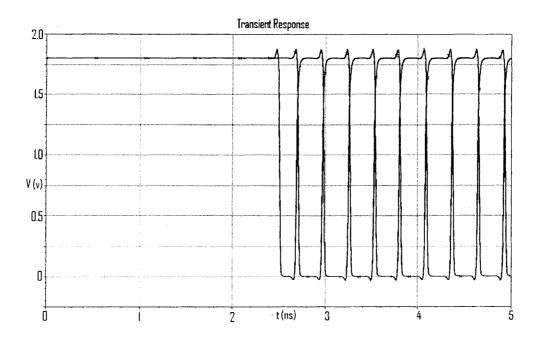

| Figure 4.22 Pre-layout simulation at the 2 <sup>nd</sup> buffer output            | 80    |

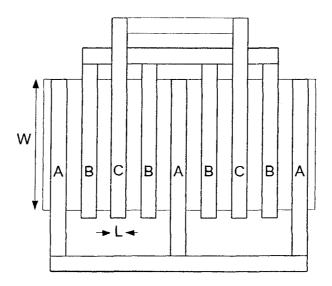

| Figure 4.23 Equivalent layout of a large-width MOSFET                             | 82    |

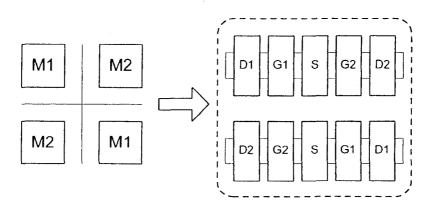

| Figure 4.24 NMOS differential pair layout using common-centroid geometry          | 82    |

| Figure 4.25 Single delay cell layout                                              |       |

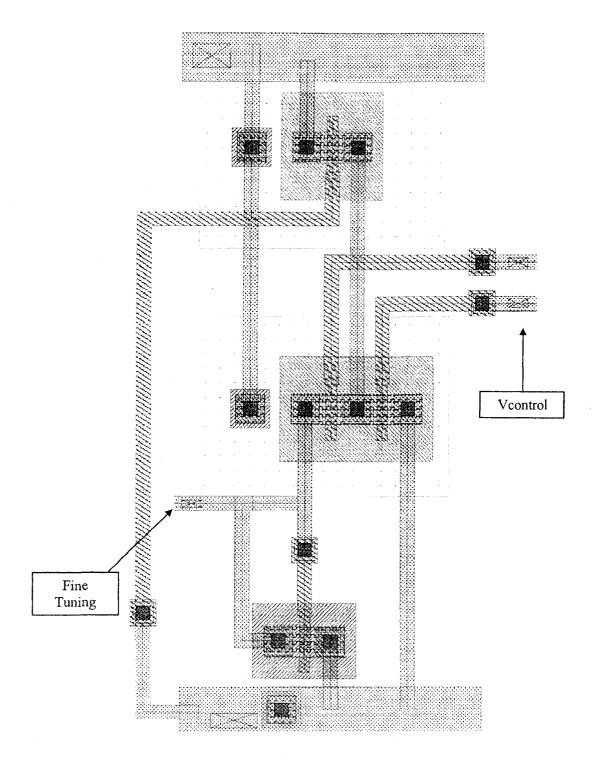

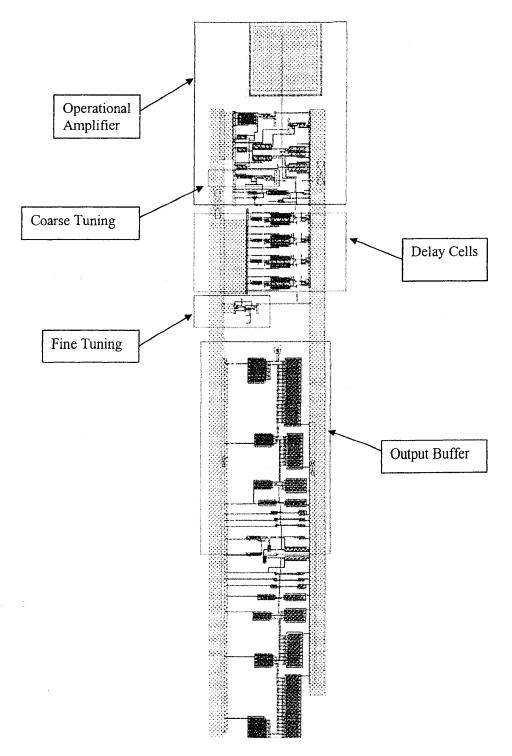

| Figure 4.26 Fine tuning layout                                                    | 85    |

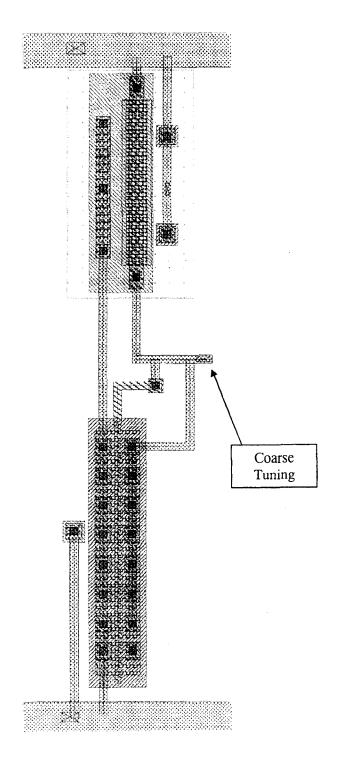

| Figure 4.27 Coarse tuning layout                                                  | 86    |

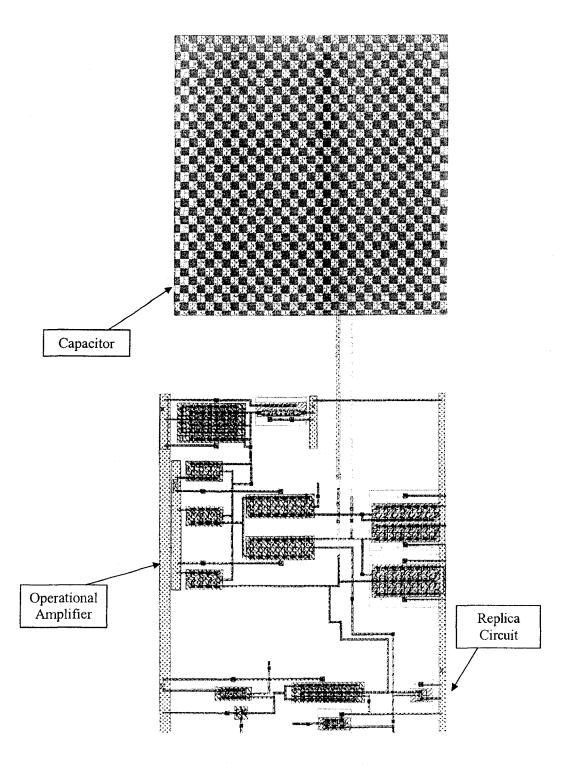

| Figure 4.28 Replica biasing layout                                                | 87    |

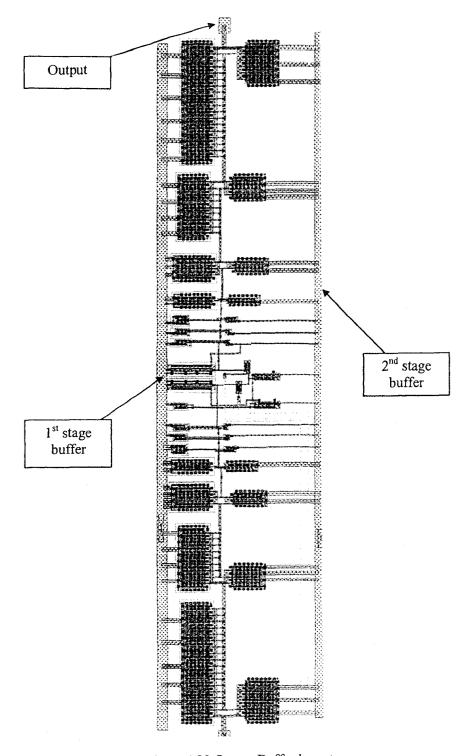

| Figure 4.29 Output Buffer layout                                                  | 88    |

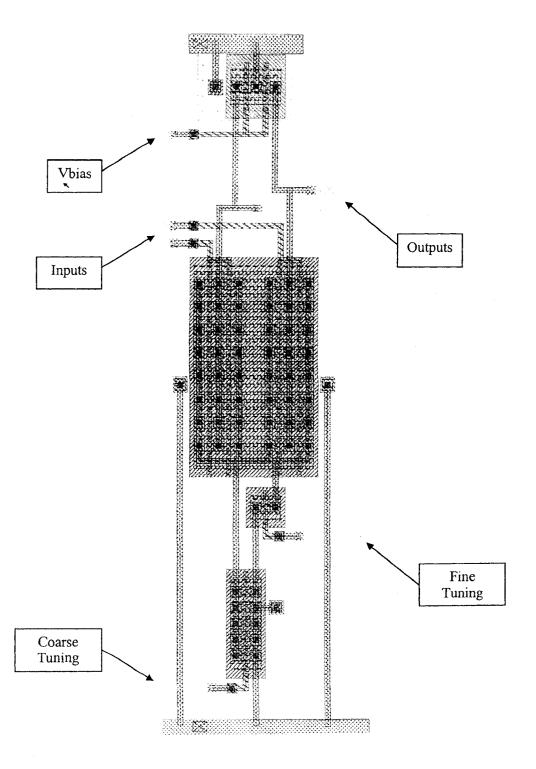

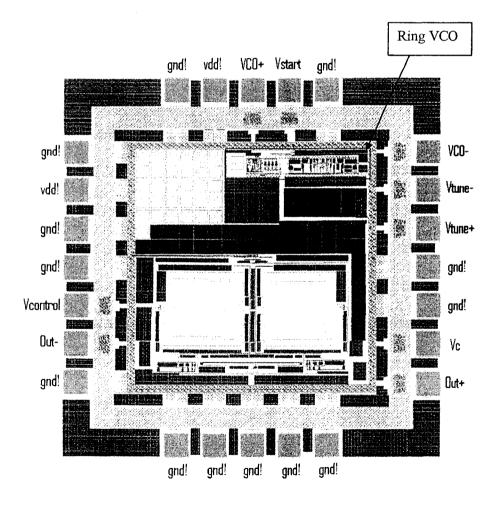

| Figure 4.30 Overall ring VCO layout                                               |       |

| Figure 4.31 Test chip layout                                                      | 90    |

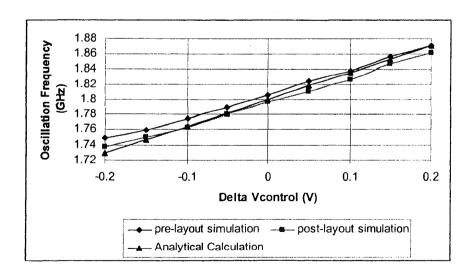

| Figure 4.32 Oscillation frequencies versus control voltages                       | 91    |

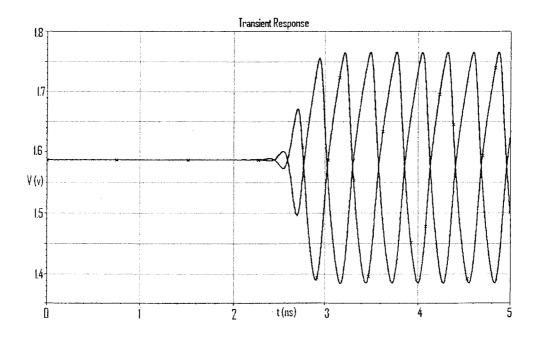

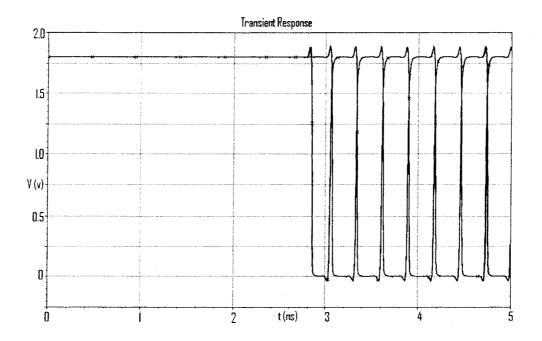

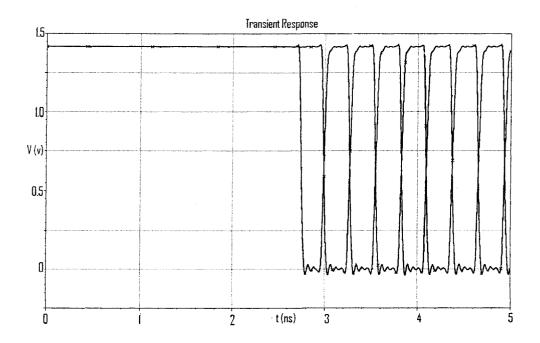

| Figure 4.33 Post-layout simulation at the 2 <sup>nd</sup> buffer output           | 92    |

| Figure 4.34 Pre-layout simulation with package, test fixture, and 50 ohm resistor | 93    |

| Figure 5.1 Companion model of a linear transconductance used in EHB               | 95    |

| Figure 5.2 Companion model of a capacitance in EHB                                | 98    |

| Figure 5.3 Companion model of a nonlinear resistor used in EHB                    | . 100 |

| Figure 5.4 Companion model of a nonlinear capacitance used in EHB                 | . 102 |

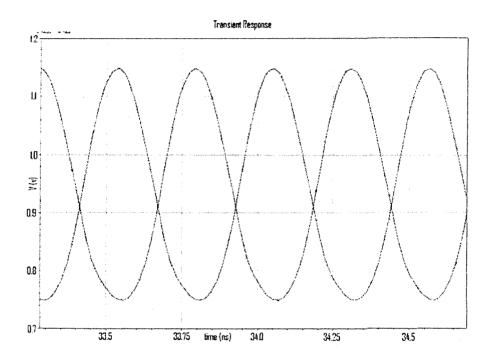

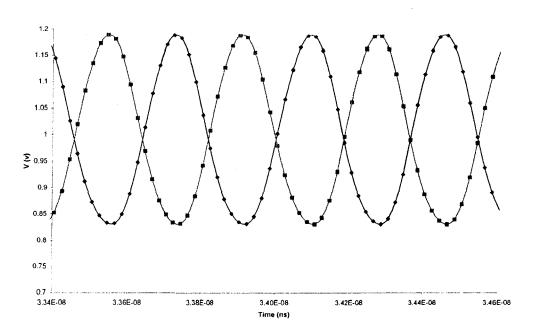

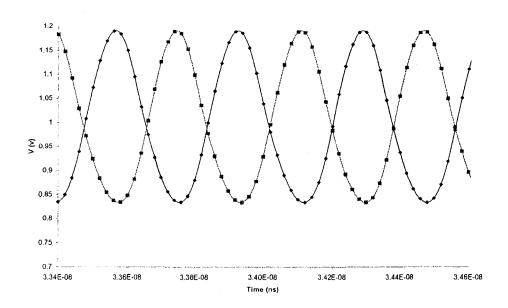

| Figure 5.5 Ring VCO output waveforms from Spectre                                 | . 103 |

| Figure 5.6 Ring VCO output waveforms from ngspice                                 |       |

| Figure 5.7 Ring VCO output waveforms from Carrot                                  | . 104 |

| Figure 5.8 Vgs vs Ids at Vmax=1e5 and (W/L=4/0.4)                                 |       |

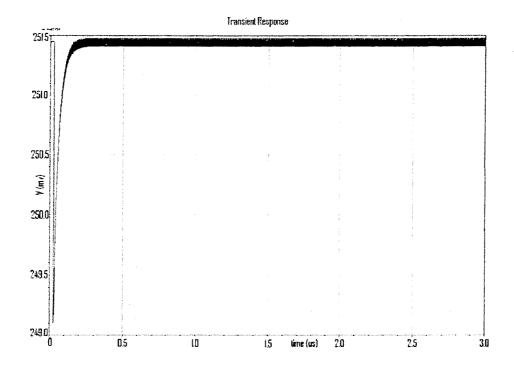

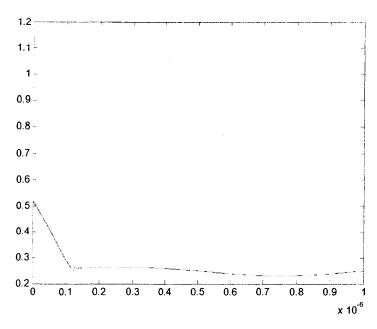

| Figure 5.9 Replica biasing voltage from Spectre                                   |       |

| Figure 5.10 Replica biasing voltage from ngspice                                  |       |

| Figure 5.11 Replica biasing voltage from Carrot                                   | . 107 |

| Figure 5.12 Replica biasing voltage with modify circuit                           | . 108 |

| Figure 5.13 VCO Opened-loop test circuit                                          |       |

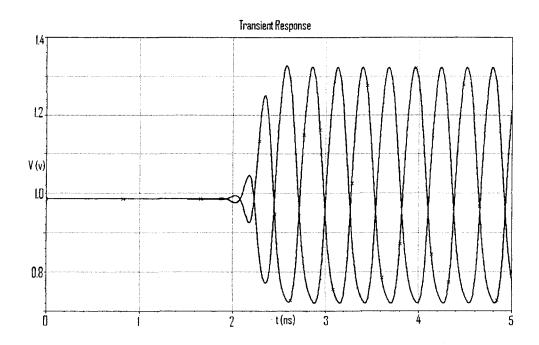

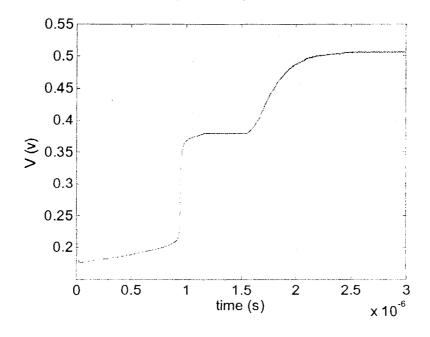

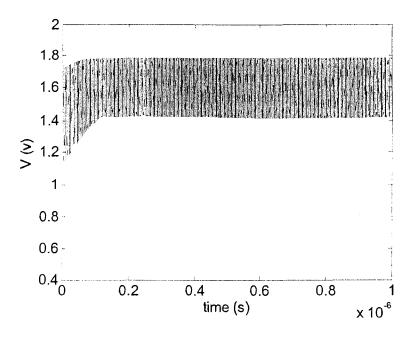

| Figure 5.14 Voltage at the delay cell using regular transient analysis            |       |

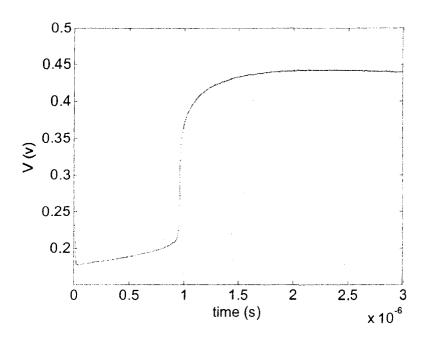

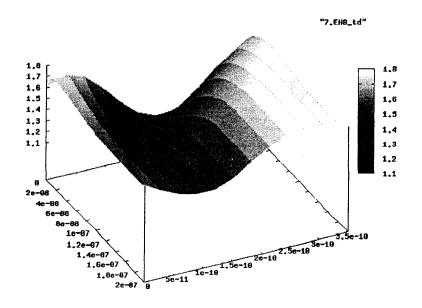

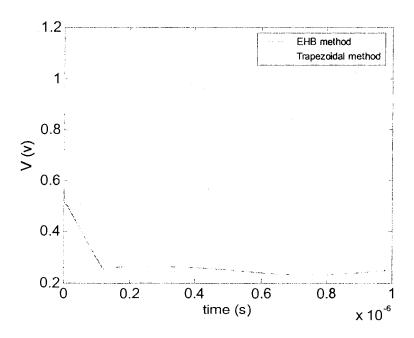

| Figure 5.15 Voltage at the delay cell output using EHB method                     |       |

| Figure 5.16 Comparison between two simulators at the replica biasing output       |       |

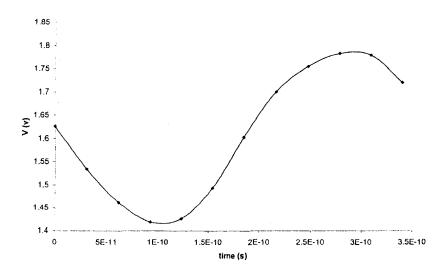

| Figure 5.17 Voltage at the delay cell output using EHB method in 2-D expression   |       |

| Figure 5.18 Voltage at the delay cell output using transient analysis             |       |

| Figure 5.18 Extracted results from EHB method at the replica bias output          |       |

| Figure A.1 Modified Tested Circuit                                                | . 118 |

| Figure A.2 Test Circuit                                                           |       |

| Figure A.3 Disconnections between Pads and Circuits                               |       |

| Figure B.1 The netlist for the closed-loop ring VCO in Carrot simulator           |       |

| Figure B.2 The netlist for the closed-loop ring VCO in ngspice simulator          | . 126 |

# List of Tables

| Table 3.1 Drain current and controlling voltages used in an n-channel MOSFET  | 25  |

|-------------------------------------------------------------------------------|-----|

| Table 3.2 Drain current and controlling voltages used in a p-channel MOSFET   |     |

| Table 3.3 Diode model parameters used in MOSFETs                              | 26  |

| Table 3.4 Threshold voltage parameters in MOSFETs                             | 28  |

| Table 3.5 Subthreshold and saturation voltage parameters in MOSFETs           | 33  |

| Table 3.6 Parasitic resistor parameters in MOSFETs                            | 39  |

| Table 3.7 Parameters used in the simplified Yang-Chatterjee charge model      | 42  |

| Table 3.8 Parameters used in the depletion capacitance                        |     |

| Table 3.9 Bulk-to-drain capacitors of p-channel and n-channel MOSFETs         | 50  |

| Table 4.1 Transistor W to L ratio in delay cell                               | 67  |

| Table 4.2 Transistor W to L ratio and resistor value in coarse tuning circuit | 69  |

| Table 4.3 Transistor W to L ratio in fine tuning circuit                      | 71  |

| Table 4.4 Transistor W to L dimensions and resistor values                    | 73  |

| Table 4.5 Transistor W to L ratio, resistor and capacitor values              |     |

| Table 4.6 Transistor W to L ratio and resistor values                         |     |

| Table 4.7 Transistor W to L ratio in the inverter chain                       | 81  |

| Table 5.1 CPU time comparison using EHB method with different sampling time   | 113 |

## List of Symbols and Abbreviations

AM Amplitude modulation Drain/Source diffusion area  $A_r$ BE Backward Euler CAD Computer-aided design Bulk-to-drain capacitance  $C_{bd}$  $C_{bs}$ Bulk-to-source capacitance CdCapacitance associated with the depleted region CFCorrection factor  $C_{gb}$ Gate-to-bulk capacitance Gate-to-bulk overlap capacitance per channel length  $C_{gba}$  $C_{gd}$ Gate-to-drain capacitance Gate-to-drain overlap capacitance per channel width  $C_{gdo}$  $C_{gs}$ Gate-to-source capacitance  $C_{gso}$ Gate-to-source overlap capacitance per channel width CJBulk-junction zero-bias bottom capacitance per area CJSWBulk-junction zero-bias sidewall capacitance per length Cox Gate-oxide capacitance per unit area **DELTA** Empirical parameter DIBL Drain-induced barrier-lowing effect EHB Envelop harmonic balance ESD Electrostatic discharge **ETA** Static feedback on threshold voltage fOscillation frequency Taylor series expansion coefficient of bulk charge  $F_{b}$ FCBulk-junction forward-bias capacitance Fs Short channel effect correction factor FM Frequency modulation Narrow channel effect correction factor FnTransconductance g **GAMMA** Body-effect parameter Transconductance gm HB Harmonic balance Drain-to-bulk current  $I_{bd}$ Bulk-to-source current  $I_{bs}$ ICS Independent current sources Drain-to-source current  $I_{ds}$ Bulk-junction saturation current  $I_{ss}$

$J_i$  Jacobian matrix

K Boltzmann's constantk Number of iterationKAPA Saturation field factor

KvcoVCO gainChannel length

$L_{eff}$  Lateral diffusion length MIM Metal-insulator-metal

MJ Bulk-junction bottom grading coefficient

MJSW Bulk-junction sidewall grading coefficient

MPDE Multi-time partial differential equation

N Number of delay cellsn Number of nodes

$n_i$  Intrinsic carrier concentration for Si

NFS

NSS

Surface state density

NSUB

Substrate doping density

ODES

Ordinary differential equations

OO Object oriented

PBBulk-junction bottom potentialPBSWBulk-junction sidewall potentialPHISurface inversion potential

PLL Phase-locked loop

$P_x$  Drain/Source diffusion perimeter

qElectronic charge $R_{ch}$ Channel resistance $R_d$ Drain ohmic resistance $R_s$ Source ohmis resistance

S Distance between the contact via and the channel

THETEmpirical coefficientTOXThin oxide thickness $t_p$ Propagation delayTJAbsolute temperaturetypeType of MOSFET

UMLUnified modeling language $U_s$ Field-related mobility reductionVVoltage drop across the diode

$V_{bi}$  Built-in voltage

$V_{bs}$  Bulk-to-source voltage

VCCSVoltage-controlled current sourcesVCOVoltage controlled oscillator $V_{ds}$ Drain-to-source voltage

$V_{fb}$  Flat band voltage

$V_{gs}$  Gate-to-source voltage

V<sub>th</sub> Threshold voltage

VMAX Maximum drift velocity of carriers

$V_{on}$  Weak inversion voltage

$V_{ov}$  Overdrive Voltage

VTO Zero-bias threshold voltage

$V_T$  Thermal voltage W Channel width

WaMPDE Warped multi-time partial differential equation

Wc Thickness of the depleted cylindrical region of the source-substrate

junction

XJ Metallurgical junction depth

$\eta$  Ideality factor  $\Phi_{ms}$  Work function

$\sigma$  Static feedback coefficient  $\rho_s$  Sheet resistance per square

$au_1$  Warped time  $au_2$  Slow time

# Chapter 1

## Introduction

#### 1.1 Motivation

Various circuit simulators are available nowadays to help IC designers shorten their design period. Designers can test their design through simulation before they put their design into the production line. However, the simulation period can be time consuming. Therefore designers should choose simulation methods with caution. In a voltage controlled oscillator (VCO) circuit for example, the oscillation frequency is determined by the input voltage. Thus, if the input voltage and output oscillation frequency are slow varying and fast varying signals respectively, the amount of samples we need to generate a period of the slow time signal is large. This can be expensive in terms of simulation time as well as memory requirements. One remedy to this problem is to treat fast and slow signals separately. Instead of using one time dimension to describe a period of the slow time signal, fast and slow signals are described in two dimensions.

The main objective in this research is to develop a tool to efficiently simulate CMOS circuits with widely separately time variations. This was accomplished by implementing MOSFET transistors models and a circuit analysis based on the MPDE technique in a general-purpose simulation program named Carrot. The MPDE approach in Carrot is implemented in an analysis type named envelope harmonic balance (EHB). A ring voltage controlled oscillator (VCO) was implemented and designed as a case study. The VCO was first designed using the software provided by Cadence and was fabricated through TSMC (Taiwan Semiconductor Manufacturing Corporation). The tools developed in this thesis were used to analyze the VCO.

#### 1.2 Overview

A literature review of MOSFET models, Multi-time simulation method, Object oriented (OO) program architecture, and concepts of companion models are given in Chapter 2. In Chapter 3, the implemented MOSFET models including both DC and AC components are explained. The ring VCO design procedures are given in Chapter 4 along with the simulation results. Due to errors in our design, we were not able to test our circuit so the experimental data is not available. The detailed design errors are given in Appendix A. Chapter 5 compares the performance of the EHB analysis using regular transient analysis as a reference. Since the MOSFET model is not suitable to describe the small geometry transistors built in the ring VCO as discussed in Chapter 4, similar ring VCO topology was redesigned using larger transistors. The design values are documented in Appendix B. The last chapter concludes the thesis and proposes the direction of future work.

# Chapter 2

# Literature Review

#### 2.1 Introduction

Circuit simulators are essential tools for IC designers as they can predict the physical behaviour of circuits. A circuit simulator usually contains two parts: models and analyses. Models include basic electronic components such as resistors, capacitors, inductors, diodes, transistors and different sources. Models describe the physical behaviour of electronic components using mathematical formulas. Designers should understand what limitations are behind each model and select them carefully to meet design requirements. MOS transistors are one of the components that have been studied extensively after the size of transistors has been scaled down both vertically and horizontally. As the MOS technology trend goes toward nano-meter era, new models appeared to accurately represent the physical behaviour of MOSFETs. DC, AC, and transient analyses are three most commonly used methods to simulate circuits. Transient analysis consists in solving a system of ordinary differential equations (ODEs) in the time domain but it takes a long time to generate signals such as amplitude modulation (AM) signals and frequency modulation (FM) signals [2]. Thus, a multiple-time scale concept [1] is introduced to solve this problem by reducing number of required sampling points so that a shorter computation time is achieved. Multi-time partial differential equation (MPDE), Envelop harmonic balance (EHB), and Warped multi-time partial differential equation (WaMPDE) are methods under the multi-time scale category. This topic is discussed in Section 2.3.

As we mentioned above, each program simulator contains device models as well as analysis methods. In this chapter, the MOSFET models are explained in chronological order in Section 2.2. To further understand how components are implemented in circuit

simulators, concepts of companion models [12, 28] for linear and nonlinear elements are discussed. The architecture of the program simulator is very important as well because a program simulator should be maintained and modified easily if necessary. Lastly, object oriented (OO) practice [21] is one of the techniques being used in many program simulators so we will explain OO techniques which have been applied to some circuit program simulator.

## 2.2 MOSFET Modeling

Using mathematical models to predict MOS transistor behaviour has been intensively developed for a few decades. The MOS model infrastructure can be categorized into three generations.

The first-generation models are referred to Level 1, Level 2, and Level 3 models. Level 1 model is known as the Schichman-Hodges model [3] which is a simplified version of long-channel devices. Due to its simplicity, it is mainly used in quick hand calculation. Level 2 model is the Geometry-based model [4] and it takes several short-channel effects into account. The main drawback of this model is that the complex mathematical expression may lead to convergence problems. Level 3 model is a semi-empirical model [5], and it is also a simplified version of Level 2. Since this model is easier to handle compared to Level 2, it still remains popular.

The second-generation models include BSIM, HSPICE, and BSIM2 which shifted the focus to circuit simulation and parameter extraction. BSIM stands for Berkeley Short-Channel IGFET Model [6], also referred to as Level 4. It relies on empirical parameters and polynomial equations to handle various physical effects and placed less emphasis on the exact physical formulation. HSPICE (Level 28) [7] is developed by Meta-Software, Inc. and is currently owned by Avant. The model eliminates the negative conductances and derivative discontinuities in BSIM model so it becomes very suitable for analog

circuit design. BSIM2 [8] is an extension version of BSIM. Even thought it repairs problems in BSIM, it is not widely used as parameters are many and very empirical.

The third-generation models are constructed from the usage of a single equation to describe I-V and C-V characteristics along with smooth functions. It solves convergence and discontinuity problems around transition regions. Models are comprised of BSIM3, BSIM4, and EKV Model. BSIM3 model has evolved into three versions: BSIM3v1, BSIM3v2, and BSIM3v3. The first two have many mathematical problems. These are solved by the third one. This model features mobility reduction, carrier velocity saturation, substrate current, subthreshold current, parasitic resistance effects, etc. [9]. BSIM4 is a more advanced model in the BSIM family and many improvements are made over BSIM3 in I-V modeling of intrinsic transistor, noise modeling, extrinsic parasitics, etc. [10]. The EKV model is developed at the Swiss Federal Institute of Technology in Lausanne [11]. The model is uniquely designed from different approaches such that all the voltages are referenced to the substrate contact rather than the source contact. Based on this idea, the model structure is simplified with fewer physical parameters.

#### 2.3 Multi-Time Simulation Methods

Transient analysis is a commonly used method to examine the dynamic behaviour of circuits whose signals are changing with respect to time. The initial condition is either defined by the user or determined from DC operating point analysis. The transient solutions are determined by solving the ordinary differential equations governing the circuit in the time-domain over a specific time period using a time-marching approach. However, this method becomes inefficient when two or more widely time-separated signals appear in the circuit. Many circuits appear to have this characteristic and VCOs are considered as an example. If a slow time-varying signal appears at the input of a VCO and its output signal is fast time-varying, lots of sampling points are required to cover a period of the slow time-varying signal and this results in an expensive computational cost. One solution to this problem is to separate fast and slow variations into different axes

corresponding to different time scales. We are introducing some methods that are based on this idea.

#### 2.3.1 MPDE

MPDE (Multi-time Partial Differential Equation) uses at least two time axes to represent signals with widely separated rates in circuits. Examples are switched-capacitor filters, mixers and switching power converters. Traditional numerical solution of such circuits is difficult to obtain because circuit behaviours vary in different rates. We will use a two-tone quasi-periodic signal [1] as an example to explain how effective this method is compare to the traditional transient analysis. The signal consists of fast and slow time-varying signals at 50KHz and 1KHz respectively so there are 50 fast-varying sinusoids with a period of 20us modulated by a slow-varying sinusoid with a period of 1ms. This two-tone quasi-periodic signal is given as

$$y(t) = \sin\left(\frac{2\pi}{T_1}t\right)\sin\left(\frac{2\pi}{T_2}t\right) \tag{2.1}$$

With traditional transient analysis, if one period of fast time-varying signal contains n sample points, the total number of samples needed for one period of the slow modulation is  $n \cdot (T_2/T_1)$ . If n is equal to 20, total number of samples was 1000. This signal is shown in Fig. 2.1. If we transfer this signal into multi-time representation

$$\overline{y}(t_1, t_2) = \sin\left(\frac{2\pi}{T_1}t_1\right)\sin\left(\frac{2\pi}{T_2}t_2\right)$$

(2.2)

Fewer undulations and sample points are needed to characterize this signal. If 20 points were used in each signal, 400 samples were needed to plot both signals on a uniform 20x20 grid. This corresponding two-periodic bivariate waveform is given in Fig. 2.2.

Figure 2.1 Example of two-tone quasi-periodic signal y(t)

Figure 2.2 Example of two-periodic bivariate waveform

This method replaces the derivative of the system ODEs by

$$\frac{dx(t)}{dt} = \frac{\partial \overline{x}(t_1, t_2)}{\partial t_1} + \frac{\partial \overline{x}(t_1, t_2)}{\partial t_2}$$

(2.3)

where  $t_1$  and  $t_2$  represent fast time and slow time respectively

The main advantage of using this method is that it requires fewer sample points compared to the traditional transient analysis so less computation time is required. The above example indicates that this method is used to solve amplitude modulation (AM) signal when two signals have wide-separated rates. Expression y(t) can be recovered by simply setting  $t_1 = t_2 = t$  in  $y(t_1, t_2)$ . However, this method is not efficient to solve frequency modulation (FM) signal referred to autonomous systems such as oscillators. Thus, the WaMPDE method is introduced next.

#### 2.3.2 WaMPDE

WaMPDE (Warped Multi-time Partial Differential Equation) also uses at least two time axes to represent signals with widely separated rate in the circuit. Unlike an AM signal, the carrier frequency in the FM signal varies with time and this implies that the number of undulations along with the fast time axis will change with time. WaMPDE warps the fast time scale as a function of the slow time so the frequency is normalized to a constant value. The derivatives in the ODE are replaced by

$$\frac{dx(t)}{dt} = \omega(\tau_2) \frac{\partial \overline{x}(\tau_1, \tau_2)}{\partial \tau_1} + \frac{\partial \overline{x}(\tau_1, \tau_2)}{\partial \tau_2}$$

(2.4)

where  $\tau_1$  and  $\tau_2$  are the warped time and the slow time, respectively.  $\omega(\tau_2)$  is an unknown warping function and is set to impose a smooth phase condition along the real

time axis. The result of WaMPDE is a multi-time partial differential equation in warped and real time scale, together with a warped function describing the relation of the two time axes. Consider a two-tone quasi-periodic FM signal shown in Fig. 2.3 [1]

$$x(t) = \cos(\varphi(t)) = \cos(2\pi f_0 t + k\cos(2\pi f_2 t))$$

(2.5)

with  $f_0 = 1MHz$  and  $f_2 = 20KHz$  and modulation index  $k = 8\pi$ . The local frequency or instantaneous frequency is modulated by a slow sinusoidal signal

$$f(t) = \frac{1}{2\pi} \cdot \frac{\partial \varphi(t)}{\partial t} = f_0 - kf_2 \sin(2\pi f_2 t)$$

(2.6)

Figure 2.3 Example of the FM signal

We can see that the FM signal is hard to analyze with a two dimensional graph. Let's analyze this FM signal using MPDE method as the fast time and slow time axis represent the oscillation and modulation signals respectively.

The FM signal with multi-time axes is

$$\overline{x}(t_1, t_2) = \cos(2\pi f_0 t_1 + k \cos(2\pi f_2 t_2))$$

(2.7)

Fig. 2.4 gives a bivariate waveform along both axes. Since many undulations appear in both axes, the MPDE method is not suitable for analyzing FM type signal.

Figure 2.4 Example of the FM signal using MPDE method

If we resolve Eq (2.7) using WaMPDE method, the fast time  $t_1$  is replaced by the warped time  $t_1$  to normalize the local frequency and  $t_2$  represents the slow time in real time domain. The new multivariate representation is

$$\overline{x}(\tau_1, \tau_2) = \cos(\tau_1) \tag{2.8}$$

and the warped time becomes a function of time

$$\tau_1 = \phi(\tau_2) = 2\pi f_0 \tau_2 + k \cos(2\pi f_2 \tau_2)$$

(2.9)

Eq. (2.8) expresses the FM signal as a function of warped and unwarped time scales. The warped time scale changes the time axis according to a time change to even out the period of the fast undulations. The result of this WaMPDE representation Fig. 2.5 also shows smooth curves on both axes.

Figure 2.5 Example of the FM signal using WaMPDE method

The results of local frequency are similar between two warped time function. The WaMPDE is efficient to simulate FM signal when two frequencies vary at widely separated rate.

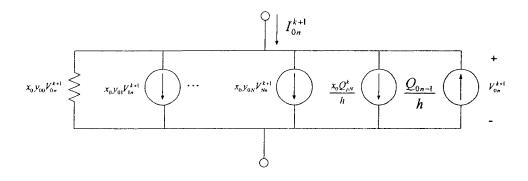

#### 2.3.3 EHB

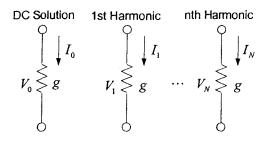

EHB (Envelope Harmonic Balance) [12] is a particular case of MPDE and it uses two time axes to describe signals with widely separated rates in the circuit. It uses  $t_1$  and

$t_2$  to represent the fast and slow time axis. Solutions along the fast time axis are solved in the frequency domain using Harmonic Balance (HB) technique. Thus, a good initial guess is usually required for the HB analysis of oscillators to converge to the desired solution. The number of harmonics is usually the same for all state variables and this number is always fixed during the simulation. When a circuit presents strong nonlinearity in a certain node, lots of harmonics are needed for a particular node while other nodes do not need many harmonics. To save the computation effort, minimum harmonics are usually required for desired accuracy in each state variable. The unknowns are the Fourier Coefficients along  $t_1$  corresponding to each value of  $t_2$ . The HB technique is based on a Fourier-series expansion of state equations. The key work of HB is to express the state variable x as a Fourier series:

$$x(t_1, t_2) = \Re\left\{\sum_{k=0}^{\infty} X_k(t_2) e^{jk\omega_0 t_1}\right\}$$

(2.10)

where  $X_k$  is the Fourier coefficient of the  $k_{th}$  harmonic. Large number of harmonics improves the accuracy but slow the computational speed.

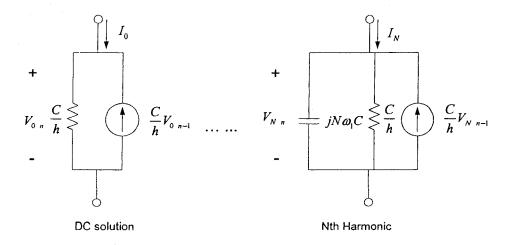

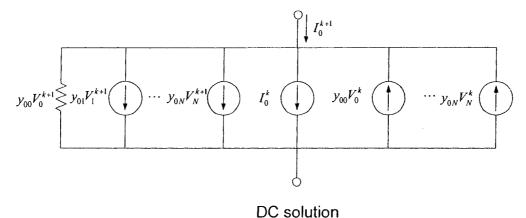

#### 2.4 Companion Models

Companion models [28] are equivalent circuits that represent each circuit component after numerical integration and Newton method are applied. The equivalent circuit can only contain DC current sources and linear transconductances. Thus, a nonlinear dynamic circuit is transformed into a linear DC circuit once the circuit elements are replaced by their companion models. In transient analysis the nonlinear differential equations that describe the circuit are converted into nonlinear algebraic equations by using numerical integration methods. Then the nonlinear algebraic equations are solved by the Newton-Raphson iteration method. This method finds a better estimate solution to the nonlinear equation after each iteration. Circuit components fall into two categories: linear and nonlinear. In addition they are further classified as static or dynamic

components. In this section, we describe some commonly used companion models in circuit simulators.

#### 2.4.1 Linear Transconductances

The current in each branch is given by

$$i = g \cdot v \tag{2.11}$$

where g is a transconductance. i and v are current and voltage respectively. The companion model of a transconductance is shown in Fig. 2.6.

Figure 2.6 Companion model of a linear transconductance

#### 2.4.2 Linear Capacitors

The companion model of a linear capacitor can be derived from the following expression.

$$i = C \frac{dv(t)}{dt} \tag{2.12}$$

The derivative is approximated by using the Backward Euler (BE) method

$$\frac{d\nu(t_{n+1})}{dt} \simeq \frac{\nu(t_{n+1}) - \nu(t_n)}{h} \tag{2.13}$$

Substituting Eq. (2.12) into Eq. (2.13) forms a companion model of linear capacitance

$$i_{n+1} = \frac{C}{h} \nu_{n+1} - \frac{C}{h} \nu_n \tag{2.14}$$

Since voltage  $v_n$  is known, the second term in Eq. (2.14) can be treated as an equivalent current source  $(i_{eq})$ . The voltage  $v_{n+1}$  is an unknown value, so the first term uses conductance to represent current flowing through the capacitor. The same idea is applied to express the vector form for this model. Fig. 2.7 gives the equivalent circuit for the capacitance model.

Figure 2.7 Companion model of a linear capacitor

#### 2.4.3 Non-linear Current Sources

Companion models for nonlinear current source can be derived in a similar manner described in Section 2.4.1 with the addition of Newton method. The graphical representation of a non-linear current source controlled by three voltages is given in Fig. 2.8

Figure 2.8 Non-linear current source

and its expression is given as  $i = f(v_1, v_2, v_3)$ . Apply Newton method to that and Eq. (2.15) is obtained.

$$i^{k+1} = i^k + \frac{\partial i}{\partial \nu} \left( \nu^{k+1} - \nu^k \right) \tag{2.15}$$

where k is the iteration number. Current  $i^{k+1}$  is a function of three voltages and can be expressed as  $i^{k+1} = i\left(v_1^{k+1}, v_2^{k+1}, v_3^{k+1}\right)$  and current  $i^k$  is a function of three voltages as well. The partial derivative term is a row vector which is a Jacobian. Then we can write the Eq. (2.15) into its vector form as

$$i^{k+1} = i^k + \begin{bmatrix} \frac{\partial i^k}{\partial v_1} & \frac{\partial i^k}{\partial v_2} & \frac{\partial i^k}{\partial v_3} \end{bmatrix} \begin{bmatrix} v_1^{k+1} - v_1^k \\ v_2^{k+1} - v_2^k \\ v_3^{k+1} - v_3^k \end{bmatrix}$$

The companion model of a nonlinear current source is shown in Fig. 2.9

Figure 2.9 Companion model of a nonlinear current source

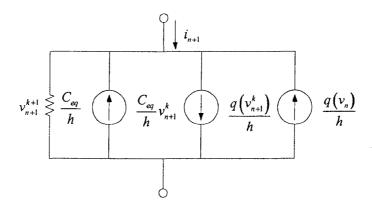

#### 2.4.4 Non-linear Capacitances

To derive the companion model for a non-linear capacitance, we consider charge as a state variable. By definition, current is equal to the derivative of charge with respect to time and the derivative term is approximated using the BE method.

$$i_{n+1} = \frac{dq(t_{n+1})}{dt} = \frac{q(v_{n+1}) - q(v_n)}{h}$$

(2.16)

The unknown term  $q(v_{n+1})$  can be solved by applying Newton method and its expression is given as

$$q(v_{n+1}^{k+1}) = q(v_{n+1}^{k}) + \frac{dq}{dv}(v_{n+1}^{k+1} - v_{n+1}^{k})$$

(2.17)

Eq. (2.18) shows the mathematical expression of the nonlinear capacitance and this is done by substituting Eq. (2.17) into Eq. (2.16).

$$i_{n+1} = \frac{C_{eq}}{h} v_{n+1}^{k+1} - \frac{C_{eq}}{h} v_{n+1}^{k} + \frac{q(v_{n+1}^{k})}{h} - \frac{q(v_{n})}{h}$$

(2.18)

The term  $\frac{dq}{dv}$  is treated as equivalent capacitance. Here, we show the graphical representation of the companion model for one nonlinear capacitance for one controlling voltage in Fig. 2.4.

Figure 2.10 Companion model for a nonlinear capacitance

## 2.5 Object-Oriented Circuit Simulators

Object-oriented (OO) programming [13] uses *objects* to design computer programs. Each object is capable of receiving, processing, and sending data to other objects. An object can be seen as a packet containing data and procedures and may be created from a template such as *class*. A class describes the functionality and behaviour of objects and each object belonging to that class is defined as an *instance*. The procedures inside objects are defined as methods which are executed by sending messages to objects.

Some important features in OO programming are inheritance, polymorphism, and encapsulation. The use of inheritance forms a class hierarchy and allows the reuse of class specifications. Polymorphism is another important feature in OO languages and it allows different object types to share the same common interface. This means that the same message sent to different instances return different results appropriate for each

specific class. In other words, the code can issue the same command to a series of objects and get appropriately different results from each one. Encapsulation treats objects as the building blocks of a complex system and specifies which classes may use members of an object. Each object exposes a certain interface and hides implementation details. UML (Unified Modeling Language) [14] is commonly used language for creating models and describing relationships between models in OO design.

APLAC [21] is an OO circuit simulator implemented in the standard C language using macros. The most important feature of this software is that circuit elements are decomposed into independent and voltage-controlled current sources. Since all models in APLAC are eventually mapped to current sources, the simple nodal analysis is all that is needed to realize nonlinear DC, AC, transient and harmonic balance analyses. Other OO circuit simulators that adopted a common interface for all the circuit elements are ACS and Sframe [15]. The code for each circuit element is separated from the rest of the program. Therefore adding new elements and algorithms to the program requires less effort. ACS and Sframe are both written in C++ and allow one element to be composed of other basic elements. The Carrot simulator [22] developed by Dr. Christoffersen is a computer program simulator runs DC, transient, and multi-time scale analyses. The OO architecture implemented in the software ensures that this software is easy to maintain while new applications are required.

#### 2.6 Reference Circuit Simulators

There are a variety of circuit simulators such as Spice, ngSpice, PSpice, Orcad and others, available in the market. We brief introduce two simulators that were used to verify results from the Carrot simulator. One is the Virtuoso Spectre circuit simulator and another is the Ngspice.

Virtuoso Spectre circuit simulator [29] is provided by Cadence and it combines the industry's leading simulation engines such as SPICE, RF and mixed-signal simulators.

It includes comprehensive device models and is capable of running DC, AC, transient analysis, sensitivity analysis, and others. The post layout verification is another important feature because designers can layout their designs for fabrication. This commercial program has become widely used among universities and industries.

Ngspice [30] is a mixed-mode, mixed signal circuit simulator used for electrical circuit design, simulation and prototyping. It is part of the EDA (electronic design automation) projects in which many people are involved. The project was started because of the lack of free EDA tools for UNIX. This simulator is based on three open source software packages: Spice3, Cider and Xspice.

Spice3 is a general-purpose circuit simulation program originating from the EECS Department of the University of California at Berkeley. It includes built-in models for discrete components such as resistors, capacitors, diodes, and transistors commonly found within integrated circuits Due to its popularity, it has become a standard for simulating circuits.

Cider is a mixed-level circuit and device simulator which was developed from Berkeley as well. It couples the latest version of Spice3 to internal C-based device simulator. It can be used to simulate all the basic types of semiconductor devices and has been ported to a variety of computing platforms.

XSpice is an extended version of the Berkeley's SPICE3 analog circuit simulator and was at the Georgia Tech Research Institute. It provides the ability to use code modeling techniques to add new models so users can create their own models by writing them in the C programming language.

# Chapter 3

# **Mosfet Model Implementation and Testing**

### 3.1 Introduction

Due to the improvement in technology, the size of MOS transistors has been scaled down in dimensions both vertically and horizontally. As the technology goes towards smaller device dimensions, the complexity of the model has increased significantly because some assumptions made in derivations of large transistors are no longer valid. Therefore, there is constant research on modeling small transistors. In general, the perspective of device modeling is to predict device performance with mathematical equations. In addition, modeling also plays an important role in the Computer-Aided Design (CAD) since it is cumbersome to analyze complex circuits using more advance models by hand calculation. Models should be chosen carefully so that their behaviour is close to the actual transistor behaviour over all regions of operation. Designers can use simulators to predict and optimize their chip performance under worst case conditions so that manufacturing tolerances can be incorporated into designs. It is imperative that designers understand the accuracy and limitation of device models in simulators so their designs will function closely to real device and development costs can be reduced.

Models can be derived using physical or empirical approaches or a combination of both. They are usually developed from basic principles and some empirical parameters are later added to improve their accuracy. Therefore, tradeoffs usually are made between the quality of approximation and its complexity. Each model works well with certain parameter values which can be obtained from device level simulator or from electrical

measurements on MOS transistors with different geometries. The accuracy of device models is fully dependent on the model parameters being used.

In this work, a semi-empirical MOS model is implemented into Carrot simulator. Even though this model is not suitable for small geometry devices, it is applicable to long-channel devices with the length greater than 2  $\mu m$  [20]. Both I-V and C-V characteristics of each component of n-channel and p-channel transistors will be described from a mathematical point of view under different operating conditions. Some correction factors are introduced to modify the existing Level 3 model to ensure smoothness between transition regions. Those correction factors are obtained from the ngSpice source code. Lastly, simulation results for both I-V and C-V characteristics are presented and results are compared against other simulator programs such as ngSpice, and Spectre. Those results indicate how close the MOS model is being implemented in the Carrot simulator compared to others.

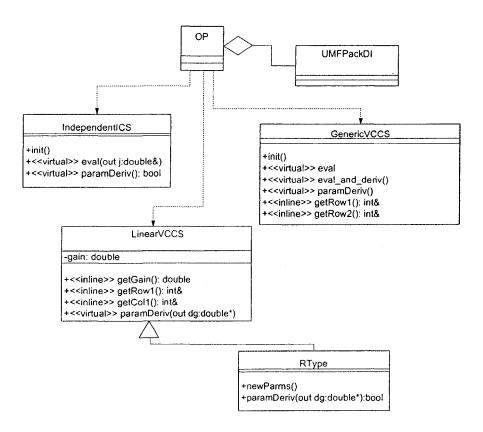

## 3.2 Circuit Simulation Program Architecture

Carrot simulator is a circuit simulator program that can perform DC, Transient, and Envelop Harmonic Balance analyses. It is modular and based on Objected-Oriented (OO) principles. New functionality can be added with no modification to the existing code. Like other simulators, it features standard circuit components such as resistors, capacitors, inductors, diodes, BJTs, MOSFETs, and voltage sources.

The transition from the circuit description to a system of equations is accomplished by decomposing each element in the circuit into either voltage-controlled current sources (VCCS) or independent current sources (ICS). To formulate the circuit equations, a similar current source approach technique as in the APLAC program [21] is used. To formulate the nodal equation at each node with different components, the companion model is applied and the system equation becomes

$$Gu(t) = S(t) \tag{3.1}$$

For example, if a circuit contains linear and nonlinear resistors, the transformation is taken care by the companion models. The above expressions demonstrate how system equations are formed and being solved from the mathematical perspective. Next, we look at how DC analysis is performed in the simulator from its UML class diagram as shown in Fig. 3.1 [22].

Figure 3.1 UML class diagram of OP class

Generic VCCS, Linear VCCS, and Independent ICS are three classes in the simulator to represent nonlinear, and linear VCCSs, and ICSs respectively. Those classes provide necessary interfaces to build the respective part of the Eq. (3.1). From the companion model point of view, the Geveraic VCCS is used for nonlinear VCCS that

requires Newton iterations. The operating point (OP) is a class that implements DC analysis using Newton method and its dependency to those classes is shown in the above UML diagram. Each class contains inline functions for efficiency where possible and different virtual functions are used for each device model. UMFPackDI is a class to solve linear systems of equations. The OP classes use the information provided by the \*CS classes to generate a linear system of equation that is solved by UMFPackDI.

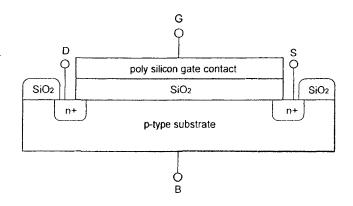

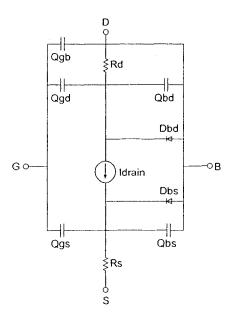

#### 3.3 DC Component Implementation

When it comes to device modeling, more complex models can predict device performance more accurately while more model parameters are required for those models. If the model parameters are not correctly specified, errors may result in device characteristics. Thus, number of unknown parameters and complexity of the model are two important factors to be taken into account when it comes to device modeling. Based on those two factors, we chose to implement the Level 3 semi-empirical model in this work. The MOSFET model required for circuit simulation can be divided into two parts: a steady-state or DC model and a dynamic or AC model. The main difference between those two models is that the former does not vary with time while the later one does. Some of the components in those two models can be further specified as intrinsic and extrinsic parts. In this section, we will discuss only DC MOS transistor models for different regions of device operation.

A basic construction of the n-channel enhancement-type MOSFET has four terminals which are referred to as drain, source, gate, and bulk. The cross section of this typical model is shown in Fig. 3.2. A p-type material is formed from a silicon base and is referred to as the substrate and two n+ regions (the source and the drain) are formed into the substrate. The gate electrode is made of polysilicon on the insulator layer.

Figure 3.2 Typical enhancement-mode MOS structure

To understand this structure better, we can look at both intrinsic and extrinsic parts of this device. The DC equivalent circuit of this transistor can be seen from Fig. 3.3. For the p-channel MOSFET model, all the voltages and currents are reversed.

Figure 3.3 Intrinsic model of an n-Channel MOSFET

The extrinsic components are the voltage control current source (Idrain) and two pn junction diodes (Dbs) and (Dbd) connected between terminals from source to bulk and drain to bulk. Under forward operating conditions, it is assumed that the only current flowing through the device is the drain-source current  $(I_{ds})$  and its current-voltage (I-V) form can be expressed as  $I_{ds} = f(V_{gs}, V_{ds}, V_{bs})$ .  $V_{gs}, V_{ds}, V_{bs}$  are gate-to-source, drain-to-source, and bulk-to-source voltage respectively. Under the same operating conditions, the source and drain voltages usually keep source and drain-to-bulk pn junctions reverse biased. The current-voltage relation for both junction diodes can be defined in the same manner such as  $I_{bs} = f(V_{bs})$  and  $I_{bd} = f(V_{bd})$ . The intrinsic elements are also known as parasitic elements which are resistances at the drain, and source terminals. Those elements can limit the drive capability of the device and are usually minimized. For a long channel device, the series resistances  $R_s$  and  $R_d$  are small. However, as the channel length decreases, those two parasitic resistances can no longer be neglected.

The model equations are usually derived from an NMOS transistor under forward mode operation where drain-to-source voltage is greater than or equal to 0. Table 3.1 shows the drain current with respect to its controlling voltages under both forward and reverse operations. Under the reverse operation, the drain-to-source voltage is less than zero so the voltage is referenced to the drain terminal. The drain current is flowing form source to drain so the controlling voltages are changed accordingly. Current and Voltage values in either forward or reverse mode in the Table 3.1 are suitable for both DC and AC n-channel MOSFEF models

Table 3.1 Drain current and controlling voltages used in an n-channel MOSFET

| Mode         | $I_{ds}$          | $V_{gs}$          | $V_{ds}$         | $V_{bs}$          |

|--------------|-------------------|-------------------|------------------|-------------------|

| Forward Mode | $I_{ds}$          | $V_{gs}$          | $V_{ds}$         | $V_{bs}$          |

| Reverse Mode | - I <sub>ds</sub> | $V_{gs} - V_{ds}$ | -V <sub>ds</sub> | $V_{bs} - V_{ds}$ |

The model can be used to handle PMOS transistors as well if currents and controlling voltages are adjusted properly. All voltages are multiplied by -1 under the forward region of operation, so the current can be calculated using the NMOS equations. On the other hand, the roles of drain and source must be changed when the transistor is inverted. Table 3.2 shows modified PMOS current and controlling voltages referenced to an NMOS transistor under both operation conditions.

Table 3.2 Drain current and controlling voltages used in a p-channel MOSFET

| Mode         | $I_{ds}$          | $V_{gs}$          | $V_{ds}$         | $V_{bs}$          |

|--------------|-------------------|-------------------|------------------|-------------------|

| Forward Mode | $I_{sd}$          | $V_{sg}$          | $V_{sd}$         | $V_{sb}$          |

| Reverse Mode | - I <sub>sd</sub> | $V_{sg} - V_{sd}$ | -V <sub>sd</sub> | $V_{sb} - V_{sd}$ |

Once the currents and controlling voltages of transistors are specified, there is less chance of making mistakes when calculating currents in each model. To describe how DC models are implemented, we will use a mathematical formula to describe two pn junction diodes, drain-to-source current source, and resistors. Table 3.3 lists parameters used in the diode equations.

#### 3.3.1 Diode Model

Table 3.3 Diode model parameters used in MOSFETs

| Parameter      | Description                      | Unit   |

|----------------|----------------------------------|--------|

| $I_{ds}$       | Drain-to-source current          | (amp)  |

| $I_{ss}$       | Bulk-junction saturation current | (amp)  |

| K              | Boltzmann's constant             | (CV/K) |

| $\overline{q}$ | Electronic charge                | (C)    |

| TJ    | Absolute temperature          | (K) |

|-------|-------------------------------|-----|

| type  | Type of MOSFET                |     |

| V     | Voltage drop across the diode | (V) |

| $V_T$ | Thermal voltage               | (V) |

| η     | Ideality factor               | -   |

A simplified mathematical form of diode currents produced from those p-n junctions from bulk (substrate) to source and bulk to drain is

$$I_d = I_{ss} \left[ \exp\left(\frac{V}{\eta \cdot V_T}\right) - 1 \right] \tag{3.2}$$

$I_{ss}$  is the bulk-junction saturation current;  $\eta$  is the ideality factor which measures how close the ideal curve is to the real one; V is the voltage drop across the diode and  $V_T$  is the thermal voltage

$$V_T = \frac{K * TJ}{q} \tag{3.3}$$

To understand the amount of current flow produced at drain to source region, it is essential to specify which region is the transistor operating at. Threshold voltage is one of the most important physical parameters of a MOSFET because it defines the region at which the device starts to turn on. An estimate of threshold voltage can be obtained by extrapolating the region of a square root of  $I_{ds}$  versus  $V_{gs}$  curve for fixed  $V_s$  having maximum slope. As the device geometry is small enough to be comparable with the thickness of the depleted region, the threshold voltage is dependent on the channel width and length. Table 3.4 gives all parameters used in threshold voltage equations.

### 3.3.2 Threshold Voltage

Table 3.4 Threshold voltage parameters in MOSFETs

| Parameter     | Description                             | Unit               |

|---------------|-----------------------------------------|--------------------|

| Cox           | Gate-oxide capacitance per unit area    | $(Farad/m^2)$      |

| DELTA         | Empirical parameter                     | -                  |

| $E_{ox}$      | Permittivity of oxide                   | (Farad/m)          |

| $E_s$         | Permittivity of Si                      | (Farad/m)          |

| ETA           | Static feedback on threshold voltage    | -                  |

| Fs            | Short channel effect correction factor  | -                  |

| Fn            | Narrow channel effect correction factor | -                  |

| GAMMA         | Body-effect parameter                   | $(\sqrt{V})$       |

| LD            | Lateral diffusion width                 | (m)                |

| $L_{\it eff}$ | Lateral diffusion length                | (m)                |

| $n_i$         | Intrinsic carrier concentration for Si  | $(1/m^3)$          |

| NSUB          | Substrate doping density                | $(1/m^3)$          |

| NSS           | Surface state density                   | $(1/m^2)$          |

| PHI           | Surface inversion potential             | (V)                |

| TOX           | Thin oxide thickness                    | (m)                |

| $U_s$         | Field-related mobility reduction        | $(m^2/(V\cdot s))$ |

| $V_{bj}$      | Built-in voltage                        | (V)                |

| $V_{ds}$      | Drain-to-source voltage                 | (V)                |

| $V_{fb}$      | Flat band voltage                       | (V)                |

| VMAX          | Maximum drift velocity of carriers      | (m/s)              |

| V <sub>th</sub>                | Threshold voltage                                                                       | (V) |

|--------------------------------|-----------------------------------------------------------------------------------------|-----|

| VTO                            | Zero-bias threshold voltage                                                             | (V) |

| Wc                             | Wc is the thickness of the depleted cylindrical region of the source-substrate junction | (m) |

| Wp                             | The thickness of the depleted region on the flat source junction                        | (m) |

| XJ                             | Metallurgical junction depth                                                            | (m) |

| $\Phi_{\scriptscriptstyle ms}$ | Work function                                                                           | (V) |

| σ                              | Static feedback coefficient                                                             | *   |

The threshold voltage equation given in Eq. (3.4) takes into account the short and narrow channel effects as well as the drain induced barrier lowering effect.

$$V_{th} = V_{bj} - \sigma \cdot Vds + GAMMA \cdot Fs \cdot \sqrt{PHI - V_{bs}} + Fn \cdot (PHI - V_{bs})$$

(3.4)

The quantity  $\sqrt{PHI-V_{bs}}$  used in this equation can cause computation errors if  $V_{bs}$  becomes positive and is greater than PHI so some modifications are made as follows.

$$\begin{aligned} V_{bs} &\leq 0 \\ phibs &= PHI - V_{bs} \\ sqphbs &= \sqrt{PHI - V_{bs}} \\ V_{bs} &> 0 \\ phibs &= PHI \\ sqphbs &= \frac{\sqrt{PHI}}{1 + 0.5 \cdot \frac{V_{bs}}{PHI}} \end{aligned} \tag{3.5}$$

Then the threshold voltage equation can be rewritten as

$$V_{th} = V_{hi} - \sigma \cdot Vds + GAMMA \cdot Fs \cdot sqphbs + Fn \cdot phibs$$

(3.6)

$V_{bj}$  (the built-in voltage) is defined in Eq. (3.7). The parameter *type* represents the type of MOS transistor being selected and the value -1 is used for p-channel MOS transistor and value +1 for an n-channel MOS transistor.

$$V_{bj} = V_{fb} + type \cdot PHI = type \cdot \left(VTO - type \cdot GAMMA \cdot \sqrt{PHI}\right)$$

(3.7)

VTO is the extrapolated zero bias threshold voltage of a long and wide channel device and is usually a user defined variable. If not given, it can be obtain from Eq. (3.8).

$$type \cdot VTO = V_{fb} + type \cdot \left(GAMMA \cdot \sqrt{PHI} + PHI\right)$$

(3.8)

When the carrier concentration is the same at the surface and at the substrate in the semiconductor, this is called flat-band condition. By definition, the flat band voltage  $V_{fb}$  is the voltage difference between the gate and bulk terminals to maintain this condition and is equal to

$$V_{fb} = \Phi_{ms} - \frac{q \cdot NSS}{C_{or}} \tag{3.9}$$

$\Phi_{ms}$  and NSS are the work function and surface state density respectively. Cox (the gate-oxide capacitance per unit area) is defined by the permittivity of oxide divides and the gate oxide thickness.

$$Cox = \frac{E_{ox}}{T_{cx}} \tag{3.10}$$

GAMMA is the body effect parameter and PHI is the surface potential for strong inversion. When the strong inversion region occurs in the semiconductor, the opposite type of carrier concentration at the surface is greater than the concentration in the substrate. Eq. (3.11) and Eq. (3.12) describe those two effects where NSUB is the substrate doping for either n-channel or p-channel MOS transistor and  $n_i$  is the intrinsic carrier concentration for Si.

$$GAMMA = \frac{\sqrt{2 \cdot q \cdot E_s \cdot NSUB}}{C_{ox}}$$

(3.11)

$$PHI = 2 \cdot V_T \cdot \left(\frac{NSUB}{n_i}\right) \tag{3.12}$$

In a long-channel device, the surface potential is relatively constant over the entire channel and is independent on changes in  $V_{ds}$ , while in the short-channel device, the change in surface potential is noticeable as  $V_{ds}$  changes. When  $V_{ds}$  increases, the barrier prevents the carriers in the drain from entering the channel diminishes. This results a smaller inversion potential so the device turns on earlier. Since the barrier lowering is caused by the drain-to-source voltage, the effect is so called the drain-induced barrier-lowing (DIBL) effect.  $\sigma$  (the static feedback coefficient) is introduced to describe this effect

$$\sigma = \frac{8.15 \cdot 10^{-22} \cdot ETA}{C_{OX} \cdot L_{eff}^{3}}$$

(3.13)

A MOSFET can be defined as a short channel device if the effective channel length  $L_{\rm eff}$  is approximately equal to the source and drain junction of XJ. Due to the overlap between the gate and the drain and source junctions, the gate-bulk electrical field depletes less charge resulting in a decrease in the threshold voltage. This effect is due to a share in the total depletion charge of the channel region by the depletion layers of the

source and the drain junctions. The correction takes account of the junction curvature. The short channel effect is calculated as

$$Fs = 1 - \frac{XJ}{L_{eff}} \cdot \left[ \frac{LD + Wc}{XJ} \cdot \sqrt{1 - \left(\frac{Wp}{XJ + Wp}\right)^2} - \frac{LD}{XJ} \right]$$

(3.14)

The thickness of the depleted region on the flat source junction can be expressed as

$$Wp = XD \cdot sqphbs \tag{3.15}$$

with

$$XD = \sqrt{\frac{2 \cdot E_s}{q \cdot NSUB}} \tag{3.16}$$

Wc is the thickness of the depleted cylindrical region of the source-substrate junction and its empirical formula is given as

$$\frac{W_C}{XJ} = 0.0631353 + 0.8013292 \cdot \frac{W_P}{XJ} - 0.011107 \cdot \left(\frac{W_P}{XJ}\right)^2$$

(3.17)

MOS transistors are referred to as narrow channel devices if they have channel width on the same order of magnitude as the maximum depletion region thickness  $X_{dm}$ . Then depletion charge occurs beyond the width of the channel. This additional charge force the gate-bulk filed to increase to balance this charge. Then the threshold voltage increases too. The narrow channel effect correction factor, Fn, models this effect with an empirical parameter DELTA introduced to allow flexibility in modeling.

$$Fn = \frac{E_s \cdot DELTA \cdot \pi}{2 \cdot C_{ss} \cdot W} \tag{3.18}$$

The threshold voltage gives designers an idea when the transistor operates in the strong inversion region if its value is less than the grate-to-source voltage. On the other hand, it

is assumed that the there is zero current flow from drain to source if the above condition is false. In fact, this is not true because a concentration of electrons near the surface still exists. A small amount of current flow increases exponentially when  $V_{\rm gr}$  approaches  $V_{\rm th}$ .

#### 3.3.3 Subthreshold Voltage and Saturation Voltage

Table 3.5 Subthreshold and saturation voltage parameters in MOSFETs

| Parameter                     | Description                                        | Unit        |

|-------------------------------|----------------------------------------------------|-------------|

| Cd                            | Capacitance associated with the depleted region    | -           |

| $F_b$                         | Taylor series expansion coefficient of bulk charge | -           |

| NFS                           | Fast surface state density                         | (atoms/cm²) |

| THET                          | Empirical coefficient                              | -           |

| $V_{\scriptscriptstyle dsat}$ | Saturation Voltage                                 | (V)         |

| V <sub>on</sub>               | Subthreshold Voltage                               | (V)         |

In order to distinguish the boundary between the weak (subthreshold) and strong inversion regions, the voltage  $V_{on}$  is introduced as

$$V_{on} = V_{th} + n \cdot V_T \tag{3.19}$$

A variable n is used to help the subthreshold expression and is only calculated if the fast surface state density (NFS) is given and not equal to zero. Cd is the capacitance associated with the depleted region.

$$n = 1 + q \cdot \frac{NFS}{Cox} + Cd \tag{3.20}$$

$$Cd = \frac{GAMMA \cdot Fs \cdot sqphbs + Fn \cdot phibs}{2 \cdot phibs}$$

(3.21)

Before we explain drain current characteristics in MOS devices, we need to know whether the devices operate in the linear or saturation region. Small amount of drain voltages can induce a channel between source and drain and the channel behaves like a resistor. As the drain voltage increases further, the voltage drop across the oxide near the drain is further reduced to a level required to maintain an inversion layer. The drain voltage at which this happens is denoted by saturation voltage. At this voltage, the channel near the drain disappears and is referred to as pinch-off condition. Once the drain voltage exceeds the saturation voltage, any further increase in drain voltages will not affect the potential at the end of the inversion layer. Also the current will not change significantly under this condition because it depends on the potential drop from the beginning of the inversion layer at the source to the end of inversion layer. In this case, the potential drop remains constant. In short-channel devices, the saturation voltage is reached when the carriers reach the limit of velocity saturation which is before the pinch-off condition. If VMAX is not specified, saturation voltage is set to  $V_a$  given in Eq. (3.23) otherwise Eq. (3.22) is used.

$$V_{dsat} = V_a + V_b - \sqrt{V_a^2 + V_b^2} (3.22)$$

$$V_a = \frac{V_{gs} - V_{th}}{1 + F_h} \tag{3.23}$$

$$V_b = \frac{VMAX \cdot L_{eff}}{U_s} \tag{3.24}$$

$$F_b = F_n + \frac{GAMA \cdot F_s}{4 \cdot \sqrt{PHI - V_{bs}}} \tag{3.25}$$

$$U_s = \frac{U0}{1 + THET \cdot \left(V_{gs} - V_{th}\right)} \tag{3.26}$$

$F_b$  is the Taylor series expansion coefficient of bulk charge.  $U_s$  is the field-related mobility reduction and THET is an empirical coefficient. In the short channel device, the carrier velocity in the channel is also a function of the normal (vertical) electric-field component. Since the vertical field influences the scattering of carriers in the surface region, the surface mobility is reduced with respect to the bulk mobility.

#### 3.3.4 Drain-to-Source Current

The drain-to-source current varies as the transistor operates in different regions. Basic drain-to-source current of a MOS transistor used in this model in the linear region is

$$I_{ds} = \frac{\beta \cdot \left(V_{gs} - V_{th} - \left(1 + F_b\right) \cdot V_{ds} / 2\right) \cdot V_{ds}}{\left(1 + \frac{U_s \cdot V_{ds}}{L \cdot VMAX}\right) \cdot \left(1 + \theta \cdot \left(V_{gs} - V_{th}\right)\right)}$$

(3.27)

where  $\beta = \mu_0 \cdot Cox \cdot W/L$ . The effects of a short-channel influence the parameters  $V_{th}$ ,  $F_s$ , and  $\beta$  while the narrow-channel effects influence the term  $F_n$ . Eq. (3.27) is valid only if the maximum carrier velocity (VMAX) is not equal to zero. If the maximum carrier velocity is set to zero, the correction factor is introduced. Eq. (3.27) is rewritten as

$$I_{ds} = \frac{\beta \cdot \left(V_{gs} - V_{th} - (1 + F_b) \cdot V_{ds} / 2\right) \cdot V_{ds}}{\left(1 + \frac{U_s \cdot V_{ds}}{L \cdot VMAX}\right) \cdot \left(1 + \theta \cdot \left(V_{gs} - V_{th}\right)\right)} \cdot (CF)$$

(3.28)

$$CF = \frac{L_{\rm eff}}{L_{\rm eff} - \sqrt{KAPA \cdot XD^2 \cdot V_{\rm dsat}} \cdot \left(\frac{V_{\rm ds}}{V_{\rm dsat}}\right)^3}$$

The drain-to-source current of a MOS transistor in the saturation region is

$$I_{ds} = \frac{\beta \cdot \left(V_{gs} - V_{th} - \left(1 + F_b\right) \cdot V_{dsat} / 2\right) \cdot V_{dsat}}{\left(1 + \frac{U_s \cdot V_{dsat}}{L \cdot VMAX}\right) \cdot \left(1 + \theta \cdot \left(V_{gs} - V_{th}\right)\right)} \cdot \left(\frac{L_{eff}}{L}\right)$$

(3.29)

When the transistor is in the saturation mode, the channel pinch-off point, or the velocity pinch down point starts to move towards the source. This movement is usually referred to as the channel length modulation which is approximated by the last term of Eq. (3.29). The following expressions are used to solve the unknown term L.

$$L_{eff} - L' = \Delta L \tag{3.30}$$

$$\Delta L = \sqrt{X^2 + KAPA \cdot XD^2 \cdot (V_{ds} - V_{dsut})} - X \tag{3.31}$$

$$X = \frac{E_p \cdot XD^2}{2} \tag{3.32}$$

$$E_{p} = \frac{KAPA \cdot I_{ds} \mid V_{ds} = V_{dsat}}{G_{D} \mid V_{ds} = V_{dsat} \cdot Leff}$$

(3.33)

$$G_D = \frac{\partial I_{ds}}{\partial V_{ds}} \tag{3.34}$$

Once again if the maximum carrier velocity term is set to zero, Eq. (3.31) is replaced by the following expression

$$\Delta L = \sqrt{KAPA \cdot XD \cdot XD \cdot V_{dsat}/8} \cdot \left(V_{ds}/V_{dsat}\right)^{3}$$

(3.35)

Punchthrough is a phenomena that the  $I_D$  increases linearly with the  $V_D$  even at gate voltage below an expected threshold voltage. If  $V_{gs}$  is held constant while  $V_{ds}$  keeps increasing, the drain depletion width will touch the source depletion width causing the level of the energy barrier of the source to drop. This will cause a large amount of current flow even though the gate has been biased to turn the device off. If the condition  $\Delta L > 0.5 \cdot Leff$  is true, Eq. (3.31) is modified using the following expression

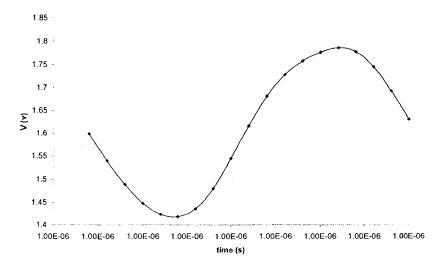

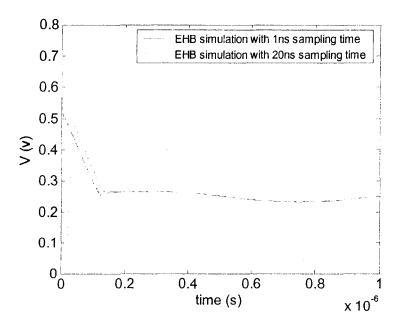

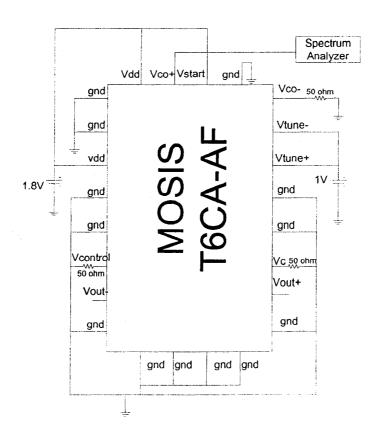

$$\Delta L = L_{eff}^3 / (4 \cdot \Delta L) \tag{3.36}$$