# DESIGN AND MODELING OF A CMOS VCO USING WAVE DIGITAL FILTERS

By

WeiBo Li

### A Thesis

Presented to Lakehead University

In partial Fulfillment of the Requirement for the Degree of

Master of Applied Science

in

Control Engineering

Thunder Bay, Ontario, Canada November 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-42163-5 Our file Notre référence ISBN: 978-0-494-42163-5

### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### **Abstract**

WEIBO LI. Design and Modeling of A CMOS VCO Using Wave Digital Filters (Under the Supervision of Dr. Carlos E. Christoffersen).

Wave digital filters (WDFs) transform an analog network into a topologically equivalent digital structure. A natural application of WDF is the simulation of electric circuits since measurements of any desired node voltages and branch currents are available during all time-steps in WDF structures. WDF structures tend to preserve most of the good properties of their analog counterpart.

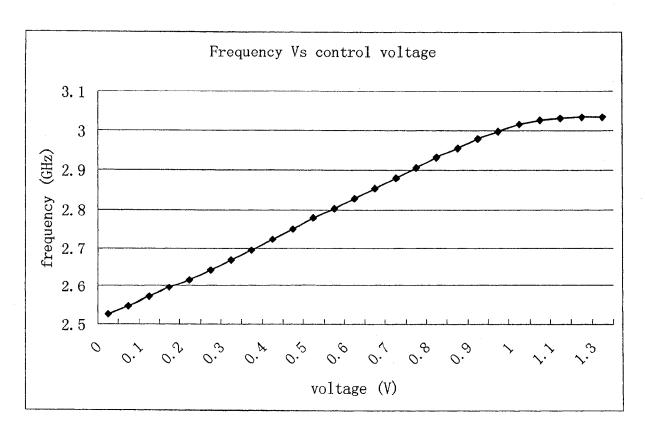

In this work, WDF techniques applied to transient simulation are studied. After a review of the basic theory of WDFs and the treatment of nonlinear elements in WDFs, WDF simulations for different circuits, including a simple RC circuit, an anharmonic oscillator and a CMOS LC voltage controlled oscillator (VCO), are presented. Special detail is put on the design and modeling of the LC VCO. The LC VCO was designed and fabricated using the TSMC (Taiwan Semiconductor Manufacturing Co., LTD) CMOS 0.18um technology. The linear frequency tuning range of the LC VCO is from 2.526 GHz to 3.015 GHz for control voltages from 0 to 1 V with a 1.712 mA tail current. WDF simulation results are compared with the exact solution if possible or otherwise with the results obtained with other simulation methods. The comparison shows that WDF techniques are efficient for the simulations of linear circuits and circuits with one nonlinear element. The potential of WDF for the simulation of large networks with many nonlinear elements is also discussed in this thesis.

### Acknowledgments

I have had the privilege of learning form Dr. Carlos E. Christoffersen during my graduate studies at Lakehead University. I would like to express my deep appreciation to his generous support, patient guidance and gentle encouragement. It was my great pleasure to study in his research group.

I also want to thank Dr. Krishnamoorthy Natarajan, Dr. Abdelhamid Tayebi and Dr. Xiaoping Liu for their enthusiastic instruction during my course study; thank Dr. M. Nasir Uddin and Dr. Zhiwei Mao for reviewing the thesis and providing instructive comments.

I wish to thank all graduate students. They give me lots of help in Matlab and course understanding.

Lastly, I would like to thank my wife and my son, Yanting Liu and Siche Li, for their endless love and encouragement.

WeiBo Li

wli12@lakeheadu.ca

### Contents

| List of Acronyms |                                   |                             |                                        |    |

|------------------|-----------------------------------|-----------------------------|----------------------------------------|----|

| Lis              | st of F                           | igures                      |                                        | vi |

| Lis              | st of T                           | ables                       |                                        | x  |

| Lis              | st of S                           | ymbols                      | S                                      | xi |

| 1                | Intro                             | duction                     | 1                                      | 1  |

|                  | 1.1                               | Moti                        | vation and Objectives of This Study    | 1  |

|                  | 1.2                               | Thesi                       | is Overview                            | 2  |

| 2                | Literature Review                 |                             |                                        | 3  |

|                  | 2.1                               | Intro                       | duction                                | 3  |

|                  | 2.2                               | 2 Scattering Transformation |                                        |    |

|                  | 2.3                               | 2.3 Bilinear Transformation |                                        |    |

|                  | 2.4                               | Linea                       | ar Building Blocks                     | 6  |

|                  |                                   | 2.4.1                       | Inductors                              | 6  |

|                  |                                   | 2.4.2                       | Capacitors                             | 7  |

|                  |                                   | 2.4.3                       | Resistors                              | 8  |

|                  | 2.5 Interconnections and Adaptors |                             | 10                                     |    |

|                  |                                   | 2.5.1                       | Parallel Adaptors                      | 10 |

|                  |                                   | 2.5.2                       | Series Adaptors                        | 12 |

|                  |                                   | 2.5.3                       | Two-Port Adaptors                      | 14 |

|                  |                                   | 2.5.4                       | Derivation of Adaptors                 | 16 |

|                  |                                   | 2.5.5                       | Trees and Kirchhoff's Laws             | 18 |

|                  | 2.6                               | Nonl                        | inear Elements in Wave Digital Filters | 23 |

|                  |                                   | 261                         | Nonlinear Resistors                    | 23 |

|   |                                                  | 2.6.2 | Nonlinear Elements with Memory                       | 25 |

|---|--------------------------------------------------|-------|------------------------------------------------------|----|

|   |                                                  | 2.6.3 | Circuits with More Than One Nonlinearity             | 30 |

| 3 | ICA                                              | /CO D | esign                                                | 31 |

| J | 3.1 Introduction                                 |       |                                                      |    |

|   | 3.2 Ring Oscillators and LC Oscillators          |       |                                                      |    |

|   | 3.3                                              | -     | CO Design                                            |    |

|   | 0.0                                              | 3.3.1 | LC VCO Topology                                      |    |

|   |                                                  | 3.3.2 | Spiral Inductor                                      |    |

|   |                                                  | 3.3.3 | NMOS Varactors                                       |    |

|   |                                                  | 3.3.4 | Tank Model Calculation Along with Simulation Results | 42 |

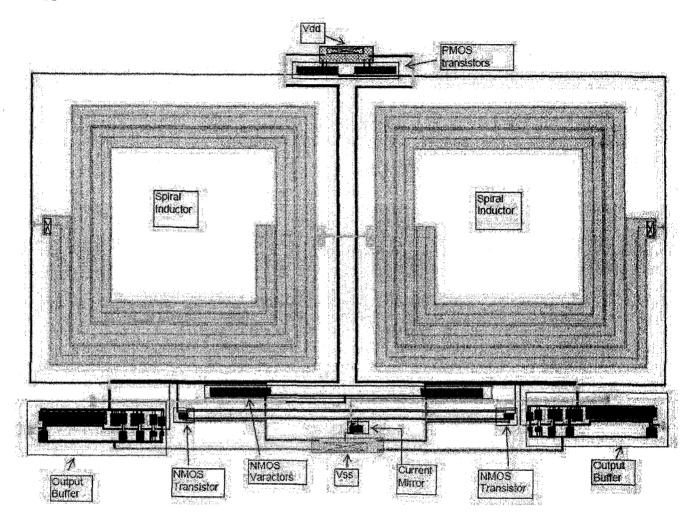

|   | 3.4                                              | Layo  | ut of the LC VCO                                     |    |

| 4 | Simulations Based on WDF Techniques49            |       |                                                      |    |

|   | 4.1                                              | Intro | duction                                              | 49 |

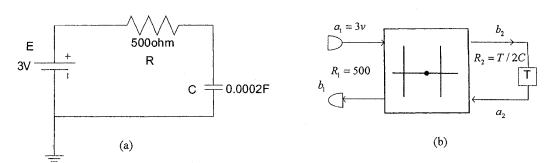

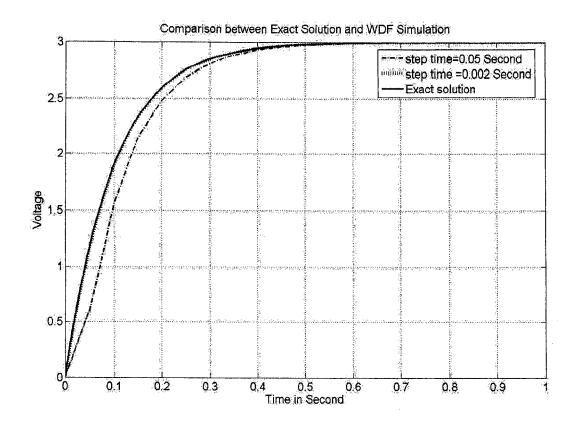

|   | 4.2                                              | Linea | ar Circuit                                           | 49 |

|   | 4.3                                              | Simu  | lation of an Anharmonic Oscillator                   | 52 |

|   | 4.4 Modeling and Simulation of an LC VCO Circuit |       | 58                                                   |    |

|   |                                                  | 4.4.1 | Simulation with Simple Inductor Model                | 61 |

|   |                                                  | 4.4.2 | Simulation with Detailed Inductor Model              | 65 |

| 5 | Conclusions and Future Work                      |       |                                                      |    |

|   | 5.1                                              | Conc  | elusions                                             | 75 |

|   | 5.2                                              | Futu  | re Work                                              | 76 |

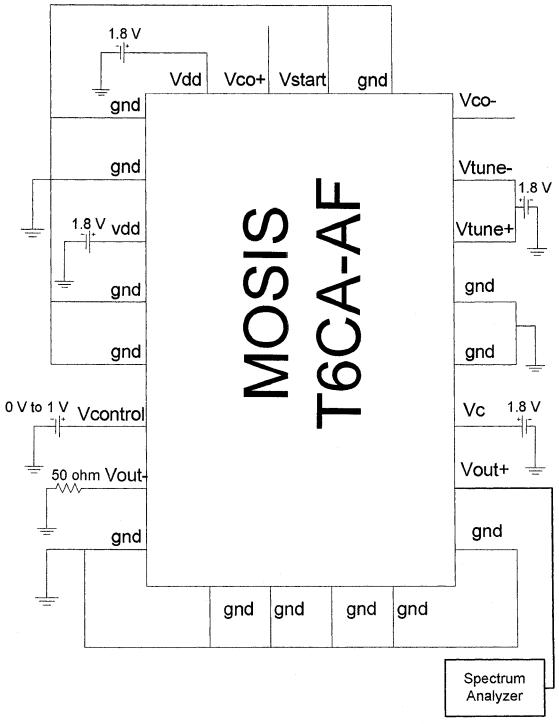

| A | The Details of LC VCO Design                     |       |                                                      | 79 |

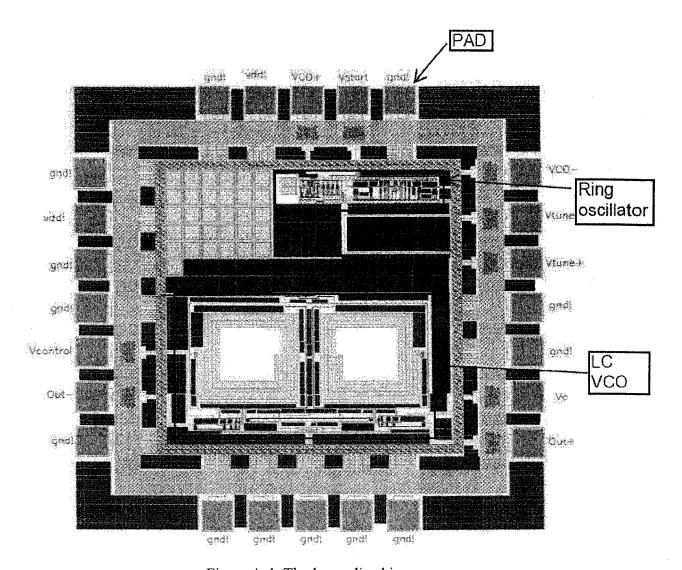

|   | A.1 Buffer Design                                |       |                                                      | 79 |

|   | A.2 Loose Die Chip                               |       |                                                      | 81 |

|   | A.3 Packaging and Fixture.                       |       |                                                      | 82 |

|   | A.4 S | imulation Results                 | 83 |

|---|-------|-----------------------------------|----|

|   | A.5 E | Experimental Results              | 86 |

| В | WDF   | Analysis of Section 4.4.2         | 88 |

|   | B.1   | WDF Analysis of Part 1 and Part 2 | 88 |

|   | B.2   | WDF Analysis of Part 3 and Part 4 | 89 |

|   | B.3   | WDF Analysis of Part 5            | 89 |

# List of Acronyms

VCO Voltage Controlled Oscillator

WDF Wave Digital Filter

TSMC Taiwan Semiconductor Manufacturing Co., LTD

KVL Kirchhoff's Voltage Law

KCL Kirchhoff's Current Law

DRC Design Rule Check

LVS Layout vs. Schematic

# List of Figures

| Figure 2.1: Spectral mapping corresponding to the Trapezoidal rule5                    |

|----------------------------------------------------------------------------------------|

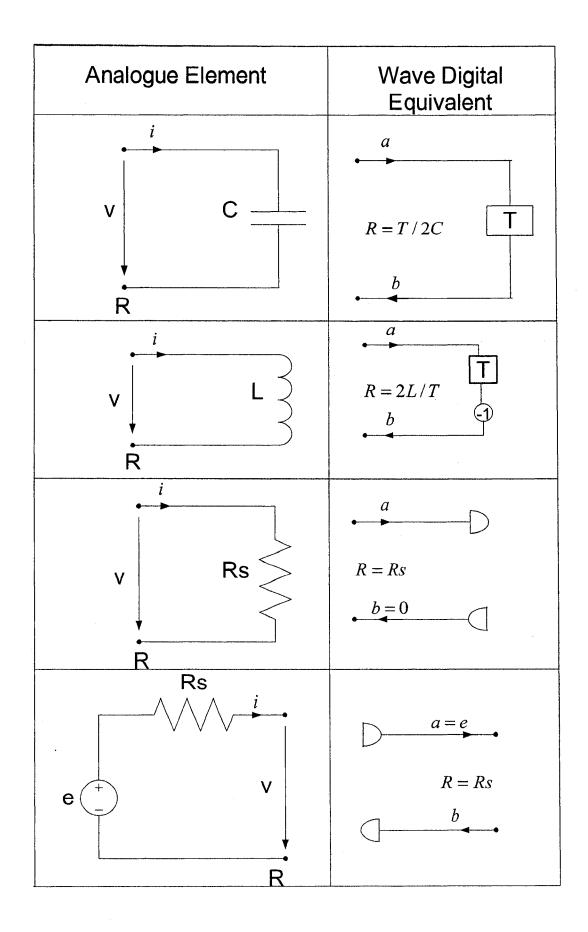

| Figure 2.2: Major elements and their realization in the WDF Domain9                    |

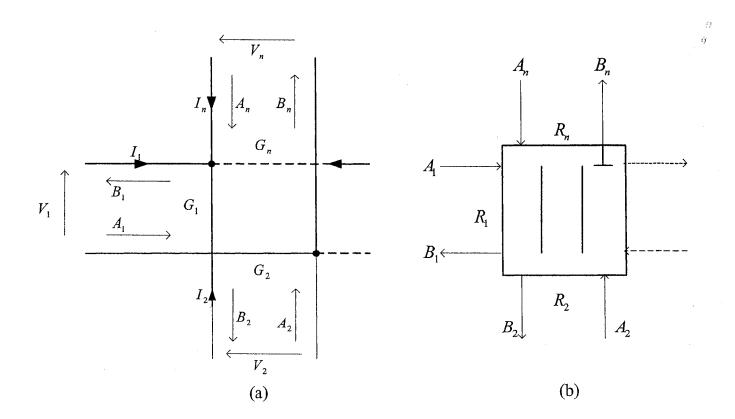

| Figure 2.3: (a) Parallel connections of n ports and (b) n-port parallel adaptor whose  |

| Port n is reflection-free                                                              |

| Figure 2.4: (a) Series connection of n ports and (b) n-port series adaptor whose Port  |

| n is reflection-free                                                                   |

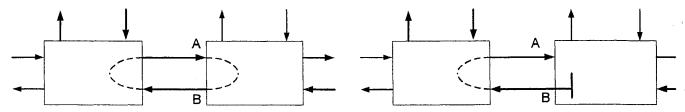

| Figure 2.5: Delay-free loop due to direct interconnection of adaptors and its          |

| interruption by a reflected-free port                                                  |

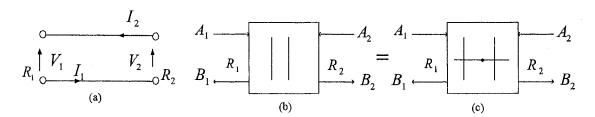

| Figure 2.6: (a) Parallel connection of two ports (b) two-port parallel adaptor (c) the |

| corresponding two-port adaptor15                                                       |

| Figure 2.7: (a) Series connection of two ports (b) two-port series adaptor (c) the     |

| corresponding two-port adaptor16                                                       |

| Figure 2.8: Wiring diagram of a bridge structure                                       |

| Figure 2.9: A connected graph                                                          |

| Figure 2.10: Graph used to illustrate the use of trees to obtain KCL and KVL           |

| equations22                                                                            |

| Figure 2.11: Scattering junction                                                       |

| Figure 2.12: (a) Direct implementation of the scattering junction (b) the simplified   |

| mode                                                                                   |

| Figure 2.13: Structure of the R-C mutator                                              |

| Figure 2.14: Structure of the R-L mutator                                              |

|                                                                                        |

| Figure 3.1: Ring oscillator topology                                                   |

| Figure 3.2: Basic LC VCO                                                               |

| Figure 3.3: The flow chart for designs by Cadence tools                            |

|------------------------------------------------------------------------------------|

| Figure 3.4: LC VCO Schematic $(V_c = V_{dd})$                                      |

| Figure 3.5: Square spiral inductor layout                                          |

| Figure 3.6: Spiral inductor equivalent circuit model                               |

| Figure 3.7: Simplified spiral inductor equivalent circuit model39                  |

| Figure 3.8: Capacitance NMOS structure with gate voltage $(V_G)$ 40                |

| Figure 3.9: Cross section of the inversion mode NMOS varactor                      |

| Figure 3.10: (a) Total capacitance of the NMOS varactor in depletion; (b)          |

| the generally assumed model of NMOS varactor42                                     |

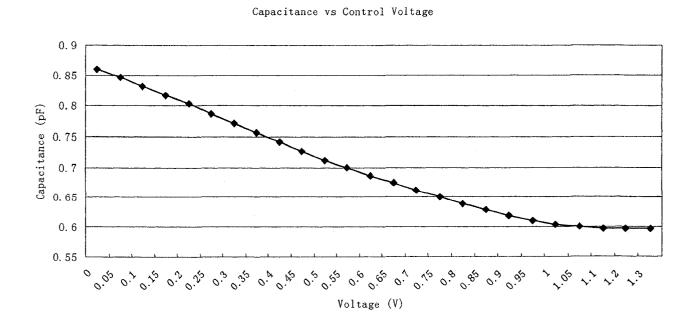

| Figure 3.11: Variable capacitance of the NMOS Varactor                             |

| Figure 3.12: The tank model of the LC VCO                                          |

| Figure 3.13: Variable capacitance of LC VCO45                                      |

| Figure 3.14: Frequency versus the control voltage                                  |

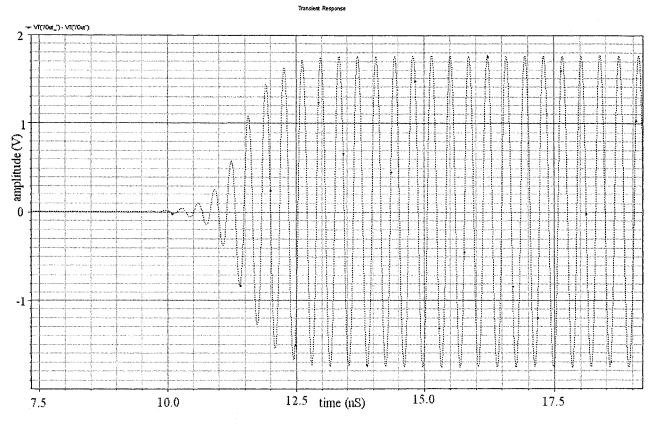

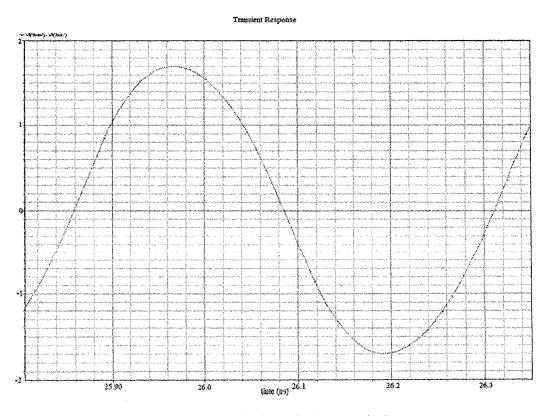

| Figure 3.15: Transient response of the LC VCO with a control voltage of 0.5 V46    |

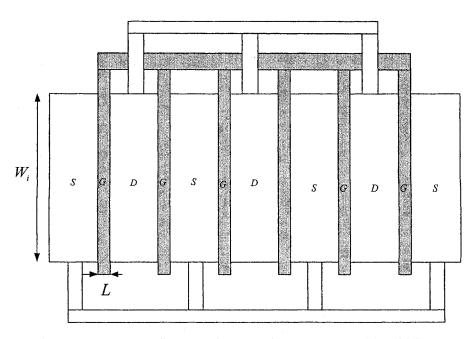

| Figure 3.16: Multi-fingered layout of a transistor with width W                    |

| Figure 3.17: The layout of the LC VCO48                                            |

| Figure 4.1: (a) RC circuit and (b) WDF implementation of the RC circuit49          |

| Figure 4.2: Comparison between exact solution and WDF simulation of                |

| the RC circuit51                                                                   |

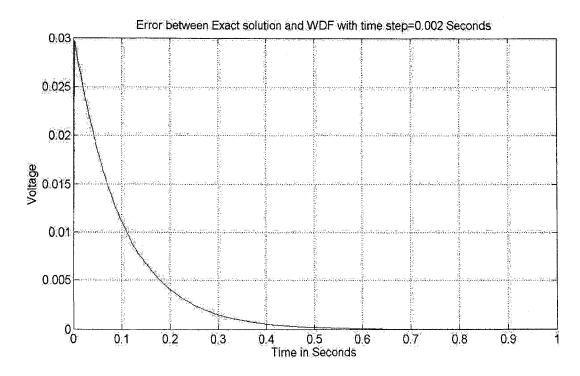

| Figure 4.3: Error plot between exact solution and WDF with $T = 0.002s$            |

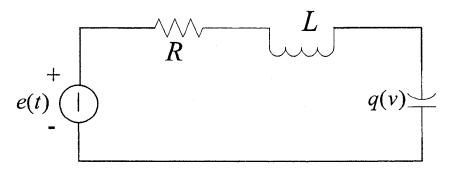

| Figure 4.4: The anharmonic oscillator circuit                                      |

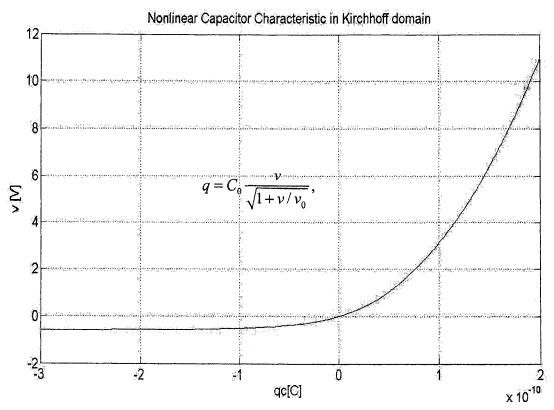

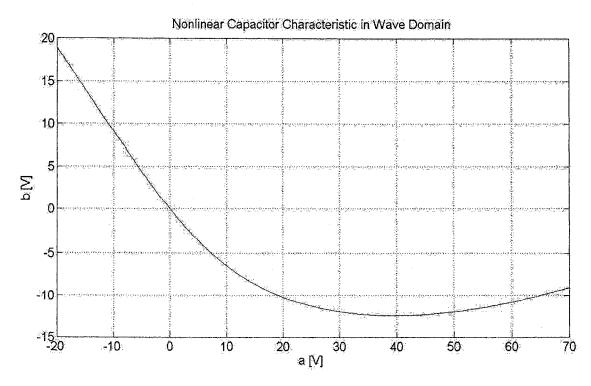

| Figure 4.5: Nonlinear characteristic of the capacitor of the anharmonic oscillator |

| in the Kirchhoff domain53                                                          |

| Figure 4.6: Nonlinear Characteristic of the capacitor of the anharmonic oscillator |

| in the wave domain53                                                               |

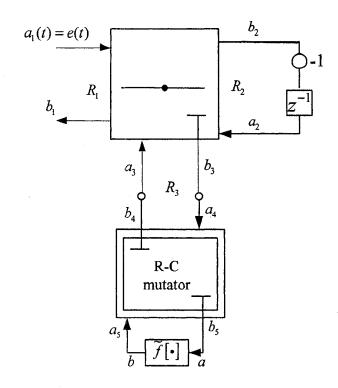

| Figure 4.7: Wave implementation of the anharmonic oscillator based                 |

| on instantaneous adaption54                                                        |

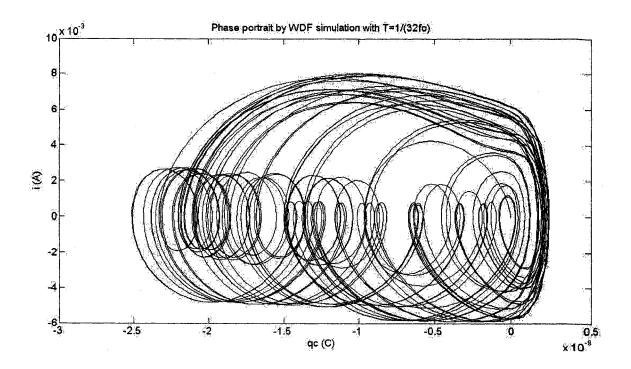

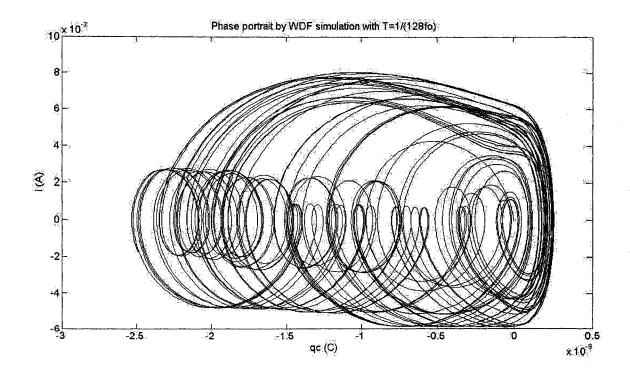

| Figure 4.8: Phase portrait of $e_0 = 3.57V$ using R-C mutator and $T=1/(32f_0)$ 50 |

| Figure 4.9: Phase portrait of $e_0 = 3.57V$ using R-C mutator and $T=1/(128f_0)$ 5 | 56    |

|------------------------------------------------------------------------------------|-------|

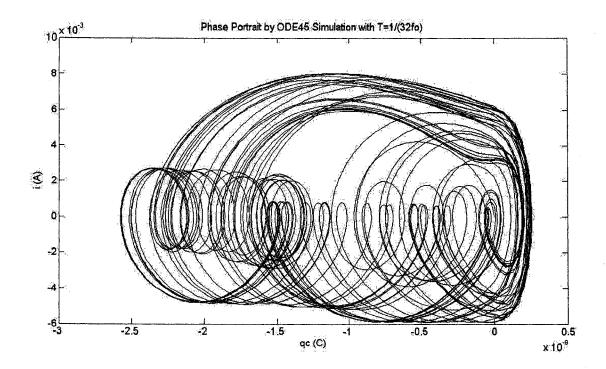

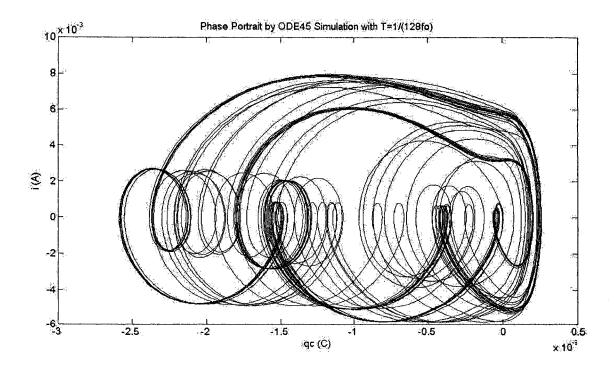

| Figure 4.10: Phase portrait of $e_0 = 3.57V$ using ODE45 and $T=1/(32f_0)$         | 57    |

| Figure 4.11: Phase portrait of $e_0 = 3.57V$ using ODE45 and $T=1/(128f_0)$        | 57    |

| Figure 4.12: Determination of the nonlinear resistor                               | 59    |

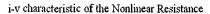

| Figure 4.13: $i-v$ characteristic of the nonlinear resistance using approximation6 | 50    |

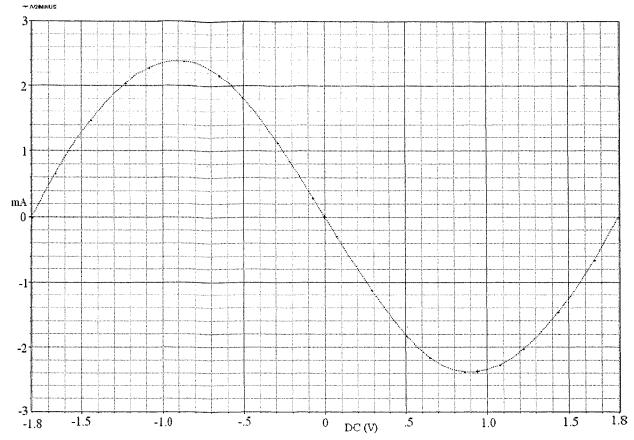

| Figure 4.14: The i-v characteristic of the nonlinear resistance using Matlab       | 50    |

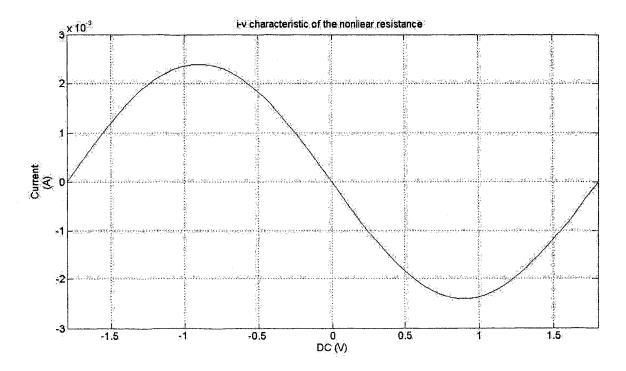

| Figure 4.15: The circuit performed in Spectre                                      | 51    |

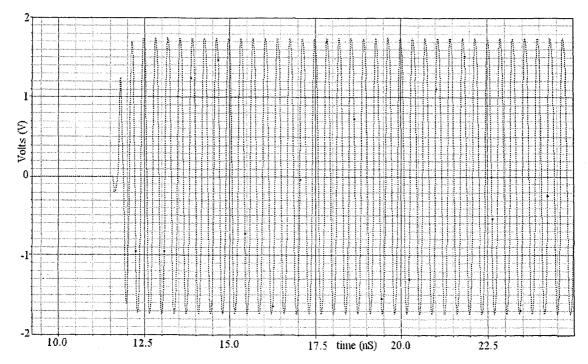

| Figure 4.16: Simulation of Fig. 4.15 in Spectre                                    | 52    |

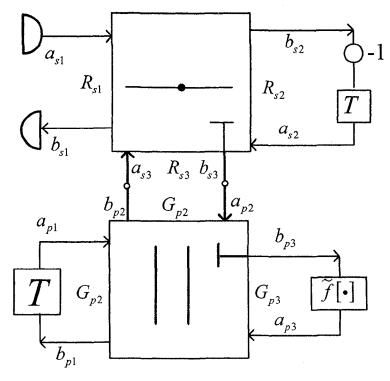

| Figure 4.17: The simplified circuit of the LC VCO                                  | 53    |

| Figure 4.18: WDF implementation of the LC VCO circuit in Fig. 4.15                 | 63    |

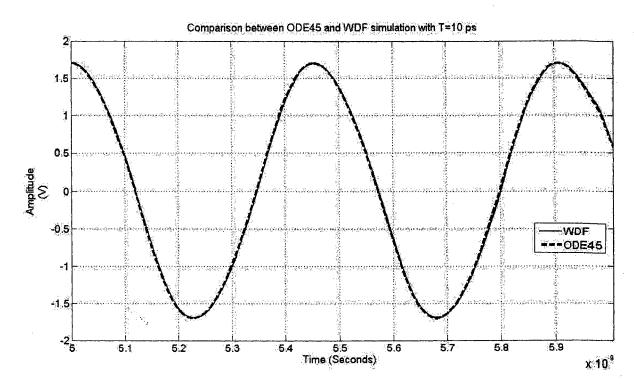

| Figure 4.19: Comparison between ODE45 and WDF simulations of the LC VCO            |       |

| simplified circuit                                                                 | 65    |

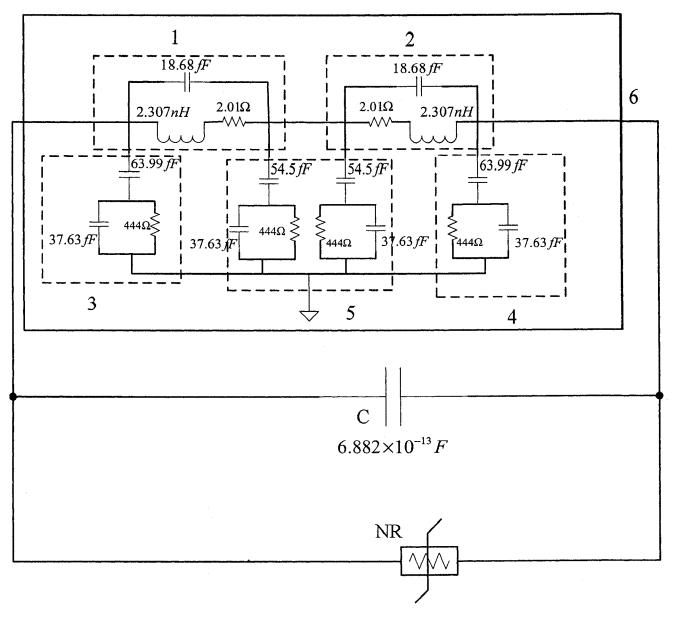

| Figure 4.20: Model of the LC VCO with equivalent models of spiral inductors        | 66    |

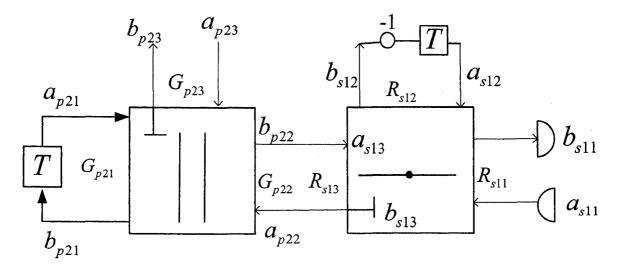

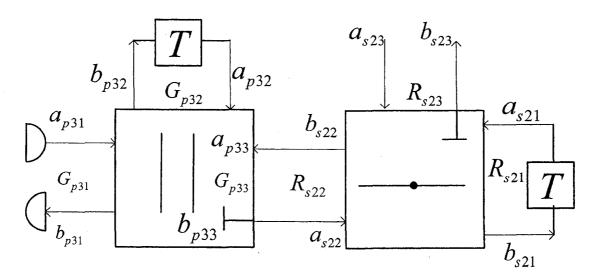

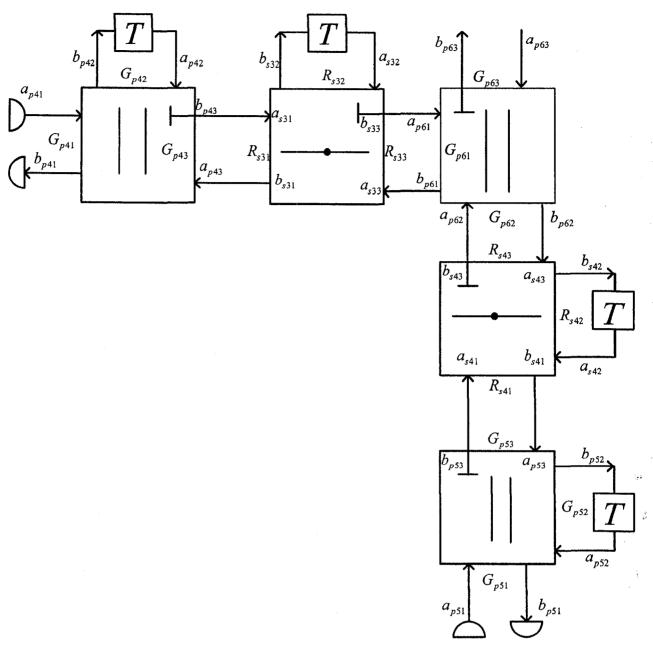

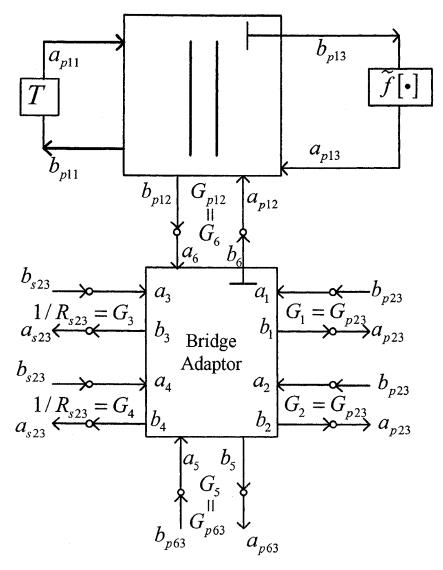

| Figure 4.21: The WDF implementation for Part 1 and Part 2                          | 67    |

| Figure 4.22: The WDF implementation for Part 3 and Part 4                          | 67    |

| Figure 4.23: The WDF implementation for Part 5                                     | 68    |

| Figure 4.24: The WDF implementation for the LC VCO with equivalent inductor        |       |

| models                                                                             | 69    |

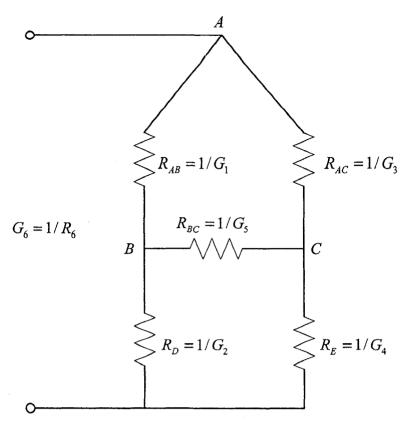

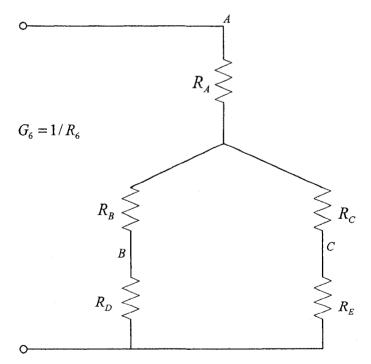

| Figure 4.25: The bridge circuit with $\Delta$ connection                           | 70    |

| Figure 4.26: The bridge circuit with Y connection                                  | 70    |

| Figure 4.27: The wiring diagram of the bridge circuit of LC VCO                    | 72    |

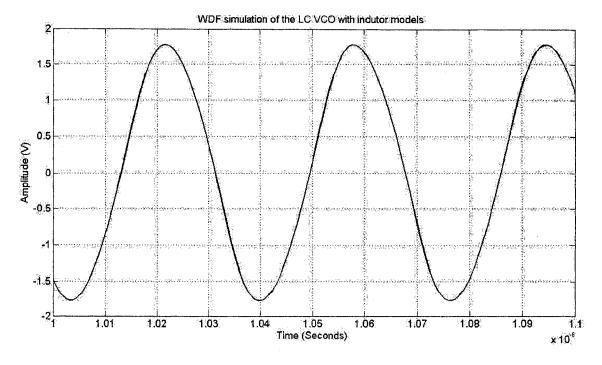

| Figure 4.28: WDF simulation result of the LC VCO model with detailed inductor      |       |

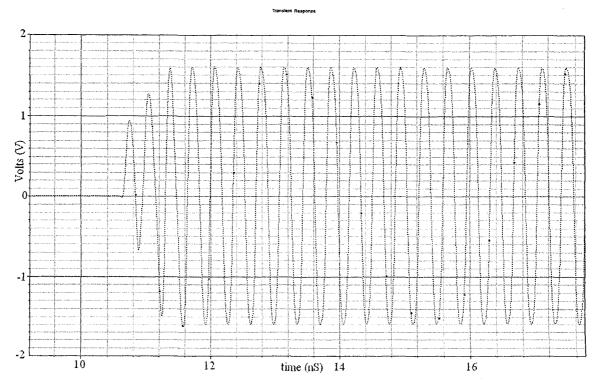

| models                                                                             | 73    |

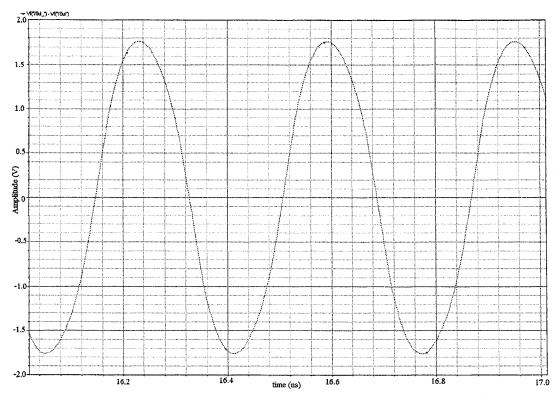

| Figure 4.29: LC VCO simulated at 0.5 V in Spectre                                  | 74    |

|                                                                                    | 76    |

| Figure 5.1: A CMOS inverter                                                        |       |

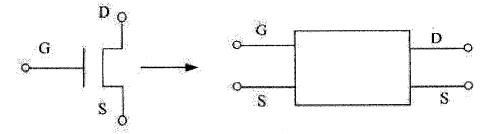

| Figure 5.2: Transistor as a two-port element                                       |       |

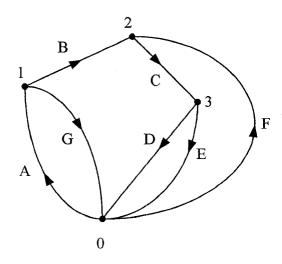

| Figure 5.3: A connected graph of the inverter                                      |       |

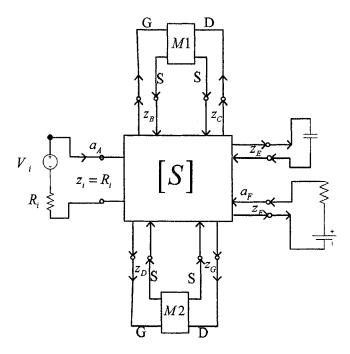

| Figure 5.4: The connection of the general adaptor                                  | . / 8 |

| Figure A.1: Output connections of the LC VCO79                                       |

|--------------------------------------------------------------------------------------|

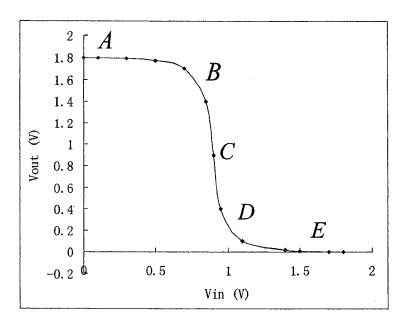

| Figure A.2: CMOS inverter transfer characteristics80                                 |

| Figure A.3: The buffer circuit80                                                     |

| Figure A.4: The loose die chip81                                                     |

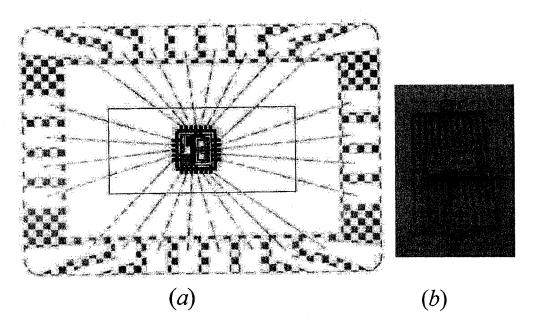

| Figure A.5: (a) The bonding diagram (b) the loose die chip with 24-pin package82     |

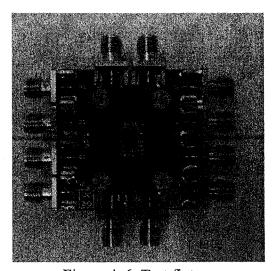

| Figure A.6: Test fixture82                                                           |

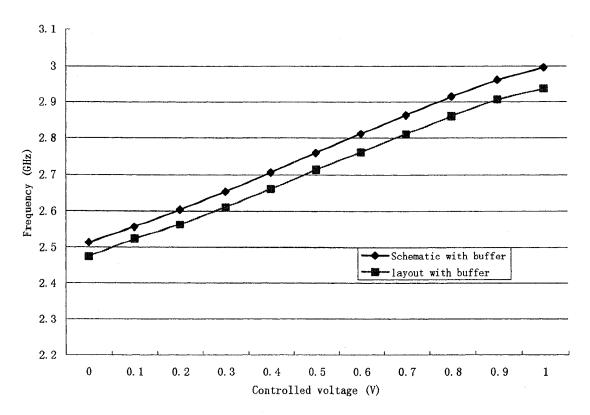

| Figure A.7: Frequency comparison between schematic and layout with buffer83          |

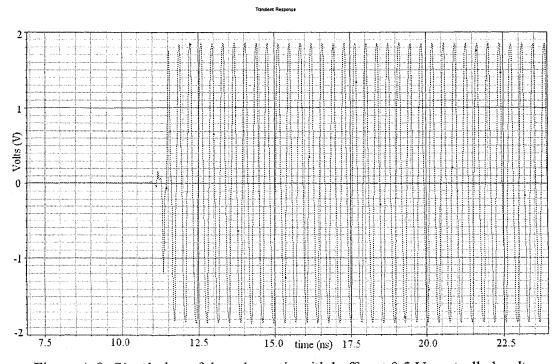

| Figure A.8: Simulation of the schematic with buffer at 0.5 V controlled voltage83    |

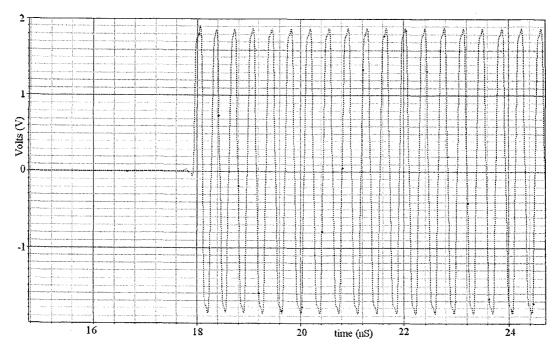

| Figure A.9: Simulation of layout with buffer at 0.5 V controlled voltage84           |

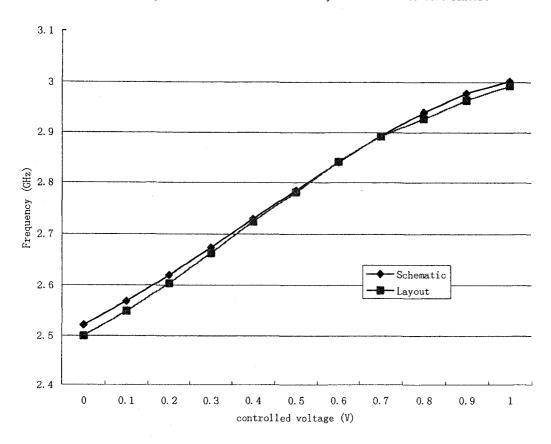

| Figure A.10: Frequency comparison between schematic and layout connected to          |

| the test fixture84                                                                   |

| Figure A.11: Simulation of the schematic with buffer connected to the test fixture85 |

| Figure A.12: Simulation of the layout with buffer connected to the test fixture85    |

| Figure A.13: The modified test fixture with package                                  |

| Figure A.14: The diagram of the tested circuit                                       |

## List of Tables

| Table 3.1: The values of spiral inductor parameters   | 38 |

|-------------------------------------------------------|----|

| Table 3.2: The sizes of transistors in LC VCO         |    |

| Table A.1: The transistor sizes of the buffer circuit | 80 |

# List of Symbols

| $A_{i}$                        | - Incident wave in z domain                       |

|--------------------------------|---------------------------------------------------|

| $B_{i}$                        | - Reflected wave in z domain                      |

| $a_i$                          | - Incident wave in time domain                    |

| $b_{i}$                        | - Reflected wave in time domain                   |

| <u>S</u>                       | - Scattering Matrix                               |

| $L_{s}$                        | - Overall inductance of spiral inductor           |

| $R_s$                          | - Conductor loss of spiral inductor               |

| $R_p$                          | -Substrate loss of spiral inductor                |

| $C_s$                          | - Overall capacitance of spiral inductor          |

| $C_{_{\scriptscriptstyle  u}}$ | - Capacitance of NMOS varactor                    |

| $C_{gd,n}$                     | - The gate-drain capacitance of NMOS transistors  |

| $C_{gs,n}$                     | - The gate-source capacitance of NMOS transistors |

| $C_{db,p}$                     | - The drain-bulk capacitance of PMOS transistors  |

| T                              | - Time step                                       |

| $\alpha$                       | - Coefficient of parallel adaptors                |

| β                              | - Coefficient of Series adaptors                  |

| $t_{j}$                        | - Discrete time                                   |

| Vc                             | - Voltage turns on and off the LC VCO             |

| $V_c$                          | - Capacitor voltage                               |

### Chapter 1

### Introduction

### 1.1 Motivation and Objectives of This Study

Simulation is a well-known technique to study complex systems. A digital signal processing methodology known as wave digital filters (WDFs) transforms an analog network into a topologically equivalent digital structure. WDFs are a natural implementation for the simulation of electric circuits. Measurements of any desired node voltages and branch currents are available during all time-steps, due to the topological relationship between the original circuit and the WDF. WDFs are well known for possessing many desirable properties over other digital filter implementations. In fact, WDF structures tend to preserve most of the good properties of their analog counterpart. For example, passivity and losslessness of analog circuits are preserved by their wave digital implementation. Furthermore, the behavior of WDFs is less sensitive to the quantization of the coefficients; therefore, WDFs exhibit modest accuracy requirements without giving up good dynamic range performance. In some situations, WDF principles can also be successfully used for modeling circuits in which a nonlinear circuit element is present under mild conditions on its characteristic. In addition, they show advantages compared with other simulation methods such as fast algorithm and simple models of electric components.

Most of the simulation methods based on the WDF principles can only solve the specific circuits or networks with only one nonlinear element. It would be of great interest to find a more efficient simulation method for large networks with more than one nonlinear element. The WDF principles show the potential to solve this problem. In addition, they also show the potential for parallel processing.

In this thesis, the goal is to study transient simulation of electric circuits based on

the WDF principles. The wave digital technique applied to circuit simulation is first reviewed. Next, some simulations in the literature are reproduced based on wave digital technique and compared with the original results in the literature and the results from other simulation methods. A CMOS LC voltage controlled oscillator (VCO) is designed and WDF principles are applied for modeling and simulating this circuit. Lastly, the simulation results are compared to see if the results are close enough.

### 1.2 Thesis Overview

The thesis is composed of five chapters. A review of the basic principles of WDFs and the transient simulation methods based on wave digital technique is presented in Chapter 2. Chapter 3 shows the design procedure and the simulation results of LC VCO. In Chapter 4, the simulations based on wave digital technique for different circuits, including the LC VCO of Chapter 3, are shown. The simulation results are discussed and compared with the exact solution or the results from other simulation methods. In the last chapter we summarize the conclusion and propose the direction of future work.

### Chapter 2

### Literature Review

### 2.1 Introduction

WDFs transform analogue network components into digital form using scattering wave variables. They were developed initially by Alfred Fettweis in the late 1960s for digitizing lumped electrical circuits composed of inductors, capacitors, resistors, transformers, gyrators and other elements of classical networks. WDFs can be considered as digital models of their continuous-time reference network. The discretization is performed by the well-known bilinear transformation and the forward and backward traveling wave quantities which are used to replace voltage and current variables.

WDFs offer a set of advantages, like coefficient accuracy, dynamic range, stability under finite-arithmetic conditions and the structure preserving implementation of the reference network.

The basic principle involved in deriving digital filters from a classical analogue network is to represent the lumped or distributed component by wave variables instead of the customary voltage and current [1, 2]. It can be divided into three steps:

- Taking each lumped component and transforming the voltage-current relationship into an incident-reflected wave relationship.

- Applying the bilinear transformation to yield a simple digital building block with one input and one output.

- Interconnecting the building blocks by using a circuit called an adaptor which is a representation of Kirchhoff's laws at a junction.

In this chapter, we first review the basic theory and concept of the WDFs, such as scattering transformation, bilinear transform, linear building blocks and adaptors.

Secondly we review the treatment of nonlinear elements in WDF. Nonlinear elements include nonlinear resistors, nonlinear capacitors and nonlinear inductors.

### 2.2 Scattering Transformation

In order to apply the bilinear transformation, it is necessary to transform voltages and currents into waves. If V denotes the voltage and I the current at a port, the waves traveling in the forward and the backward directions are defined by the following relationships [1, 2],

$$\begin{cases} A = V + RI \\ B = V - RI \end{cases} \tag{2.1}$$

where A is the incident wave, B is the reflected wave and R is a constant which has the dimensions of resistance and so will be called the port resistance.

For impedance Z, substituting V = IZ for V in Equation (2.1), the following equations are obtained,

$$\begin{cases}

A = IZ + RI \\

B = IZ - RI

\end{cases} \Rightarrow S = \frac{B}{A} = \frac{Z - R}{Z + R}$$

(2.2)

This is the reflection coefficient, S for the impedance Z. Equation (2.2) can be rewritten as B = SA. A as input, B as output and S as the transfer function which depends on impedance Z and port resistance R only.

Signal parameters A and B are chosen as linear combination of V and I. Equation (2.1) also can be expressed as follows,

$$\begin{cases} V = \frac{A+B}{2} \\ I = \frac{A-B}{2R} \end{cases}$$

(2.3)

### 2.3 Bilinear Transformation

WDFs are based on the application of bilinear transformation which is a particular type of spectral mapping between the analog frequency variable s and discrete frequency variable z [1, 3]. The bilinear transformation is a first-order approximation of the natural logarithm function that is an exact mapping of the z-plane to the s plane.

When the Laplace transform is performed on a discrete-time signal, the result is precisely the Z transform of the discrete-time sequence with the substitution of

$$z = e^{sT} = \frac{e^{\frac{sT}{2}}}{e^{\frac{sT}{2}}}$$

since  $e^{x} = 1 + x + \frac{x^{2}}{2!} + \frac{x^{3}}{3!} + \cdots$

therefore,  $z \approx \frac{1 + \frac{sT}{2}}{1 - \frac{sT}{2}}$

and  $s \approx \frac{2}{T} \frac{1 - z^{-1}}{1 + z^{-1}}$  (2.4)

T is sampling time,  $z^{-1}$  is interpreted as a unit delay of duration T. The mapping affects only reactive ports whose behavior is frequency-dependent, such as inductor and capacitor. Memoryless elements, such as transformer, gyrator and resistor which are frequency-independent, will not be affected by such a transformation.

It is important to mention that the time-domain interpretation of the bilinear mapping is called the trapezoidal rule for numerical integration. The bilinear transformation takes the left-half plane in s to the inside of unit circle in z, and the right-half plane in s to the outside the unit circle in z [27]. This is shown in Fig. 2.1. This implies that stable, causal transfer function in s will be mapped to stable and causal transfer function in the discrete variable z. In some sense, the mapping preserves passivity or energetic properties of the original system.

Figure 2.1: Spectral mapping corresponding to the Trapezoidal rule

The Trapezoidal rule for numerical integration meets the requirements of a fast solution within an acceptable precision. It presents very good characteristics in terms of low distortion and numerical stability, being A-stable [5]. Those reasons explain its choice as the basic integration rule for most general purpose simulation programs, where a great number of possible network conditions must be satisfied.

### 2.4 Linear Building Blocks

All linear elements used in classical passive analogue circuits (resistances capacitances, inductances, gyrators, ideal transformers and unit elements) and resistive sources can be digitally simulated by obeying the scattering and bilinear transformations [2, 4]. As examples, we consider only a capacitance, an inductance and a resistance.

#### 2.4.1 Inductors

Consider an inductor, for which the voltage-current relationship is shown below,

$$V = (sL)I \tag{2.5}$$

Applying the bilinear transformation Equations (2.4) to (2.5), we get

$$Z(s) = Ls = \frac{2L}{T} \frac{1 - z^{-1}}{1 + z^{-1}}$$

(2.6)

Substituting Equation (2.6) into (2.2), the following is obtained,

$$\frac{B}{A} = \frac{\frac{2L}{T} \frac{1 - z^{-1}}{1 + z^{-1}} - R}{\frac{2L}{T} \frac{1 - z^{-1}}{1 + z^{-1}} + R}$$

By setting port resistance R = 2L/T, we get

$$B = -z^{-1}A \tag{2.7}$$

As shown in Equation (2.7), the reflected wave B is equal to the incident wave A multiplying by a minus unit delay  $z^{-1}$ . In other words, the reflected wave B is equal to the negative of the previous step value of incident wave A.

The inductors can also be derived by using the trapezoidal rule which is

equivalent to applying the bilinear transformation in continuous time domain.

According to the trapezoidal rule, the inductor current can be expressed as follows,

$$i(t) = i(t-T) + \frac{1}{L} \int_{t-T}^{t} v(\tau) d\tau$$

(2.8)

Equation (2.8) is approximated by

$$i(t) = i(t - T) + \frac{T}{2L} [v(t) + v(t - T)]$$

(2.9)

According to Equation (2.3), perform the wave variables substitution into Equation (2.9),

$$v(t) = \frac{a(t) + b(t)}{2}$$

,  $i(t) = \frac{a(t) - b(t)}{2R}$

where a(t) and b(t) are the incident and the reflected waves in time domain. The result is

$$\frac{a(t) - b(t)}{2R} = \frac{a(t - T) - b(t - T)}{2R} + \frac{T}{2L} \left( \frac{a(t) + b(t)}{2} + \frac{a(t - T) + b(t - T)}{2} \right)$$

Choosing R = 2L/T to obtain the inductor instantaneous wave quantities in the time domain, we obtain:

$$b(t) = -a(t - T) (2.10)$$

Comparing Equation (2.10) with (2.7), both equations are same but in different domain.

### 2.4.2 Capacitors

For a capacitor, the voltage-current relationship is

$$V = \left(\frac{1}{sC}\right)I\tag{2.11}$$

By applying bilinear transform, we have

$$Z(s) = \frac{1}{sC} = \frac{T}{2C} \frac{1 + z^{-1}}{1 - z^{-1}}$$

(2.12)

Replacing Z From equation (2.2) in Equation (2.12),

$$\frac{B}{A} = \frac{\frac{T}{2C} \frac{1+z^{-1}}{1-z^{-1}} - R}{\frac{T}{2C} \frac{1+z^{-1}}{1-z^{-1}} + R}$$

By setting the port resistance R = T/2C, we obtain

$$B = z^{-1}A (2.13)$$

According to the Trapezoidal rule, the capacitor in the continuous time domain is shown below,

$$v(t) = v(t-T) + \frac{1}{C} \int_{t-T}^{t} i(\tau) d\tau$$

(2.14)

By using wave quantities to replace voltages and currents, we obtain:

$$\frac{a(t) + b(t)}{2} = \frac{a(t-T) + b(t-T)}{2} + \frac{T}{2C} \left( \frac{a(t) - b(t)}{2R} + \frac{a(t-T) - b(t-T)}{2R} \right)$$

By setting R = T/2C, the above equation becomes

$$b(t) = a(t - T), \tag{2.15}$$

which is the same as Equation (2.13).

#### 2.4.3 Resistors

From the voltage-current characteristic of a resistance  $R_1$ ,  $V = R_1 I$ , the equation (2.1)

becomes

$$B = \frac{R_1 - R}{R_1 + R} A \tag{2.16}$$

If the port resistance R is chosen equal to the element value  $R_1$ , we obtain

$$R = 0$$

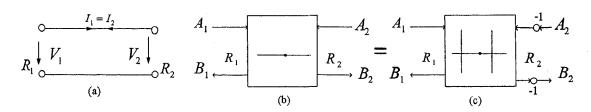

Fig. 2.2 shows the major elements and their equivalences in the WDF domain.

Figure 2.2: Major elements and their realization in the WDF Domain.

### 2.5 Interconnections and Adaptors

In order to fully establish equivalence with a classical circuit, the interconnections (Kirchhoff's laws) should be simulated. Interconnection is achieved by the use of adaptors which are digital representations of Kirchhoff's laws [1]. The adaptors of WDF are memoryless devices whose task is to perform transformations between pair of wave variables that are referred to different levels of port resistance. The most important of these adaptors are parallel adaptors and series adaptors.

### 2.5.1 Parallel Adaptors

The following figure shows a parallel connection with n ports and the symbol for parallel adaptor with one reflection-free port.

Figure 2.3: (a) Parallel connections of n ports and (b) n-port parallel adaptor whose Port n is reflection-free

The equations of the parallel connection are shown below

$$V_1 = V_2 \cdot \dots = V_n$$

$$I_1 + I_2 \cdot \dots + I_n = 0$$

The following equations are achieved for the reflected wave  $B_k$  in matrix form

$$\begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_{n-1} \\ B_n \end{bmatrix} = \begin{bmatrix} (\alpha_1 - 1) & \alpha_2 & \cdots & \alpha_{n-1} & \alpha_n \\ \alpha_1 & (\alpha_2 - 1) & \cdots & \alpha_{n-1} & \alpha_n \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ \alpha_1 & \alpha_2 & \cdots & (\alpha_{n-1} - 1) & \alpha_n \\ \alpha_1 & \alpha_2 & \cdots & \alpha_{n-1} & (\alpha_n - 1) \end{bmatrix} \begin{bmatrix} A_1 \\ A_2 \\ \vdots \\ A_{n-1} \\ A_n \end{bmatrix}$$

$$\alpha_k = \frac{2G_k}{\left(G_1 + G_2 \cdot \dots + G_n\right)}$$

$k = 1, 2, \dots n$ .  $G_k = 1/R_k$

Since  $\sum_{k=1}^{n} \alpha_k = 2$ , the coefficient  $\alpha_k$  of one of the ports, called the dependent port, can be eliminated. By choosing port n as the dependent port, the equations become,

$$\begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_{n-1} \\ B_n \end{bmatrix} = \begin{bmatrix} (\alpha_1 - 1) & \alpha_2 & \cdots & \alpha_{n-1} & 2 - \sum_{k=1}^{n-1} \alpha_k \\ \alpha_1 & (\alpha_2 - 1) & \cdots & \alpha_{n-1} & 2 - \sum_{k=1}^{n-1} \alpha_k \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ \alpha_1 & \alpha_2 & \cdots & (\alpha_{n-1} - 1) & 2 - \sum_{k=1}^{n-1} \alpha_k \\ \alpha_1 & \alpha_2 & \cdots & \alpha_{n-1} & (1 - \sum_{k=1}^{n-1} \alpha_k) \end{bmatrix}$$

If one of the coefficients  $\alpha_k$  is equal to one, the corresponding port is reflection-free. If Port n is reflection-free, i.e.,  $\alpha_n = 1$ , the reflected wave at port n is independent of the incident wave at Port n. In this case, Port n is reflection-free and Port n-1 is a dependent port. The following show the equations in matrix form.

$$\begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_{n-1} \\ B_n \end{bmatrix} = \begin{bmatrix} (\alpha_1 - 1) & \alpha_2 & \cdots & 1 - \sum_{k=1}^{n-2} \alpha_k & 1 \\ \alpha_1 & (\alpha_2 - 1) & \cdots & 1 - \sum_{k=1}^{n-2} \alpha_k & 1 \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ \alpha_1 & \alpha_2 & \alpha_3 & (-\sum_{k=1}^{n-2} \alpha_k) & 1 \\ \alpha_1 & \alpha_2 & \alpha_3 & 1 - \sum_{k=1}^{n-2} \alpha_k & 0 \end{bmatrix} \begin{bmatrix} A_1 \\ A_2 \\ \vdots \\ A_{n-1} \\ A_n \end{bmatrix}$$

### 2.5.2 Series Adaptors

Figure 2.4: (a) Series connection of n ports and (b) n-port series adaptor whose Port n is reflection-free

Figure 2.4 shows the series connection of n ports and the symbol for n-port series adaptor with Port n as reflection-free port.

The equations of the parallel connection are shown below

$$V_1 + V_2 \cdot \dots + V_n = 0$$

$$I_1 = I_2 \cdot \dots = I_n$$

The following equations are achieved for the reflected wave  $B_k$  in matrix form

$$\begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_{n-1} \\ B_n \end{bmatrix} = \begin{bmatrix} (1-\beta_1) & -\beta_1 & \cdots & -\beta_1 & -\beta_1 \\ -\beta_2 & (1-\beta_2) & \cdots & -\beta_2 & -\beta_2 \\ \vdots & -\beta_3 & \ddots & -\beta_3 & -\beta_3 \\ -\beta_{n-1} & -\beta_{n-1} & \cdots & (1-\beta_{n-1}) & -\beta_{n-1} \\ -\beta_n & -\beta_n & \cdots & -\beta_n & (1-\beta_n) \end{bmatrix} \begin{bmatrix} A_1 \\ A_2 \\ \vdots \\ A_{n-1} \\ A_n \end{bmatrix}$$

$$\beta_k = \frac{2R_k}{R_1 + R_2 \cdots + R_n} \qquad k = 1, 2, \dots n.$$

If Port n is chosen as a dependent port to eliminate the corresponding  $\beta_n$ , since  $\sum_{k=1}^n \beta_k = 2$ , we obtain the following,

$$\begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_{n-1} \\ B_n \end{bmatrix} = \begin{bmatrix} (1-\beta_1) & -\beta_1 & \cdots & -\beta_1 & -\beta_1 \\ -\beta_2 & (1-\beta_2) & \cdots & -\beta_2 & -\beta_2 \\ \vdots & \vdots & \ddots & -\beta_3 & -\beta_3 \\ -\beta_{n-1} & -\beta_{n-1} & \cdots & \vdots & \vdots \\ \sum_{k=1}^{n-1} \beta_k - 2 & \sum_{k=1}^{n-1} \beta_k - 2 & \cdots & \sum_{k=1}^{n-1} \beta_k - 2 & \sum_{k=1}^{n-1} \beta_k - 1 \end{bmatrix} \begin{bmatrix} A_1 \\ A_2 \\ \vdots \\ A_{n-1} \\ A_n \end{bmatrix}$$

Setting Port n as reflection-free and Port n-1 as dependent port, the equations are as shown below,

$$\begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_{n-1} \\ B_n \end{bmatrix} = \begin{bmatrix} (1-\beta_1) & -\beta_1 & \cdots & -\beta_1 & -\beta_1 \\ -\beta_2 & (1-\beta_2) & \cdots & -\beta_2 & -\beta_2 \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ \sum_{k=1}^{n-2} \beta_k - 1 & \sum_{k=1}^{n-2} \beta_k - 1 & \cdots & \sum_{k=1}^{n-2} \beta_k & \sum_{k=1}^{n-2} \beta_k - 1 \\ -1 & -1 & \cdots & -1 & 0 \end{bmatrix} \begin{bmatrix} A_1 \\ A_2 \\ \vdots \\ A_{n-1} \\ A_n \end{bmatrix}$$

The series and parallel adaptors fully establish equivalence between the modeled network and its digital implementation. For this reason, the concept of reflection-free ports is important to assure that a WDF can be realized. The solution of non-linear and time varying circuits without a reflection-free port would require an iterative numerical method, which is time consuming and inadequate for real-time simulation. Also, the interconnection of two adaptor ports without a reflection-free port would create a delay-free directed loop [3]. This is shown in Fig. 2.5. As we can see from Fig. 2.5, the reflected wave B depends on the instantaneous incident wave A, and the incident wave A also depends on the instantaneous reflected wave B. This creates a delay-free loop that makes the WDF unrealizable. In the delay-free loop, the wave B depends on the unknown wave A which also depends on the unknown wave B. Thus, it is impossible to calculate wave B in one iteration and the WDF becomes unrealizable. When a reflection-free port is introduced, the reflected wave B does not depend on the incident wave A anymore. This makes the WDF realizable.

Figure 2.5: Delay-free loop due to direct interconnection of adaptors and its interruption by a reflected-free port

#### 2.5.3 Two-Port Adaptors

The simplest adaptors are those with n=2. They are of particular importance in the design of WDFs [6]. We consider first a parallel connection of two ports with port resistance  $R_1$  and  $R_2$ . From the parallel adaptor equations, the following equations are obtained if Port 2 is dependent

$$B_{2} = A_{2} - \alpha_{1}(A_{2} - A_{1})$$

$$B_{1} = B_{2} + (A_{2} - A_{1})$$

$$\alpha_{1} = \frac{2R_{2}}{R_{1} + R_{2}}$$

If Port 1 is chosen as dependent port, we obtain the follows,

$$B_{1} = A_{1} - \alpha_{2}(A_{1} - A_{2})$$

$$B_{2} = B_{1} + (A_{1} - A_{2})$$

$$\alpha_{2} = \frac{2R_{1}}{R_{1} + R_{2}}$$

A more symmetrical way of writing the above equations is

$$B_{1} = A_{2} + \alpha (A_{2} - A_{1})$$

$$B_{2} = A_{1} + \alpha (A_{2} - A_{1})$$

$$\alpha = \frac{(R_{1} - R_{2})}{(R_{1} + R_{2})}$$

(2.17)

We also have

$$\alpha = 1 - \alpha_1 = \alpha_2 - 1$$

The symmetrical way introduces the equations of two-port adaptor. The symbol of two-port adaptor is shown in Fig. 2.6(c).

Figure 2.6: (a) Parallel connection of two ports (b) two-port parallel adaptor (c) the corresponding two-port adaptor

As two ports connected in parallel can also be considered to be connected in series, the adaptor is also a series two-port adaptor. One might expect two-port series and two-port parallel adaptors to be the same. This is essentially true, but the orientation of voltage and current at one of the ports, say Port 2, has to be reversed if one passes from the parallel to the series connection. This can be seen from Fig. 2.6(a) and Fig. 2.7(a).

Since the voltage and current are reversed, the corresponding wave quantities signs should be changed. Fig. 2.7(b) and (c) shows the relations between two-port series adaptor and two-port adaptor.

For the two-port series adaptor, the reflection coefficients are given as follows,

$$\beta_{1} = \frac{2R_{1}}{R_{1} + R_{2}}$$

$$\beta_{2} = \frac{2R_{2}}{R_{1} + R_{2}}$$

$$\alpha = \beta_{1} - 1 = 1 - \beta_{2}$$

Figure 2.7: (a) Series connection of two ports (b) two-port series adaptor (c) the corresponding two-port adaptor

### 2.5.4 Derivation of Adaptors

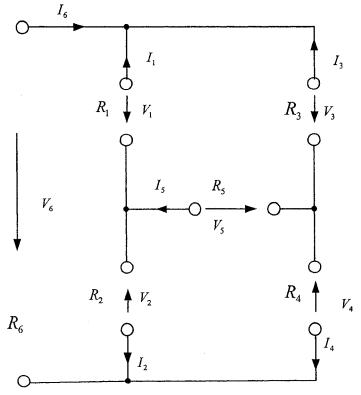

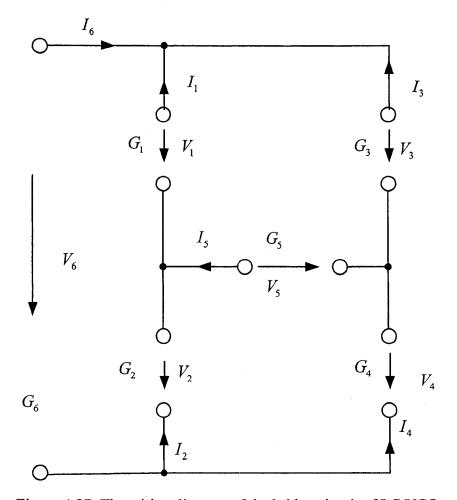

Figure 2.8: Wiring diagram of a bridge structure

Generally adaptors may be derived from Kirchhoff's laws. As an example, the scattering matrix of a lattice adaptor is calculated [7]. Fig. 2.8 depicts the corresponding wiring diagram of a bridge structure. The definitions of the wiring diagram are given

$$V = [V_{1}, \dots, V_{6}]^{T}$$

$$\vec{I} = [I_{1}, \dots, I_{6}]^{T}$$

$$\vec{A} = [A_{1}, \dots, A_{6}]^{T}$$

$$\vec{B} = [B_{1}, \dots, B_{6}]^{T}$$

$$\underline{G} = diag\left(\frac{1}{R_{1}}, \dots, \frac{1}{R_{6}}\right)$$

$$\begin{cases} V_{1} - V_{2} - V_{6} = 0 \\ V_{1} - V_{3} + V_{5} = 0 \\ V_{2} - V_{4} + V_{5} = 0 \end{cases}$$

$$\begin{cases} I_{1} + I_{3} + I_{6} = 0 \\ I_{3} + I_{4} + I_{5} = 0 \end{cases}$$

With the above definitions, voltage and current rules from the bridge structure can be written as

$$\underline{M_{\nu}} = \begin{bmatrix} 1 & -1 & 0 & 0 & 0 & -1 \\ 1 & 0 & -1 & 0 & 1 & 0 \\ 0 & 1 & 0 & -1 & 1 & 0 \end{bmatrix} \Leftrightarrow \underline{M_{\nu}} \vec{V} = \vec{0}$$

$$\underline{M_I} = \begin{bmatrix} 1 & 0 & 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 1 & 0 & -1 \\ 0 & 0 & 1 & 1 & 1 & 0 \end{bmatrix} \Leftrightarrow \underline{M_I} \vec{I} = \vec{0}$$

In the case of vectors, the equations (2.3) of voltages and currents related to the wave quantities may be written as

$$\vec{V} = \frac{\vec{A} + \vec{B}}{2} \Rightarrow \underline{M_{V}} (\vec{A} + \vec{B}) = \vec{0}$$

$$\vec{I} = \underline{G} \frac{\vec{A} - \vec{B}}{2} \Rightarrow \underline{M_{I}} \underline{G} (\vec{A} - \vec{B}) = \vec{0}$$

$$\Rightarrow \left[ \frac{M_{V}}{M_{I} \underline{G}} \right] \vec{A} + \left[ \frac{M_{V}}{-M_{I} \underline{G}} \right] \vec{B} = \vec{0}$$

$$\Rightarrow \vec{B} = \underline{S} \vec{A} \Rightarrow \underline{S} = -\left[ \frac{M_{V}}{-M_{I} \underline{G}} \right]^{-1} \left[ \frac{M_{V}}{M_{I} \underline{G}} \right]$$

(2.18)

In the above derivation, Kirchhoff's laws describe an interconnection in the voltage and current domain. These equations are transformed to the scattering matrix  $\underline{S}$  that describes the interconnection in the WDF domain by equivalence.

#### 2.5.5 Trees and Kirchhoff's Laws

As we can see from the equation (2.18), the most important part is to obtain the matrices  $\underline{M}_{v}$  and  $\underline{M}_{i}$ . It would be a problem to obtain the matrices for a large network.

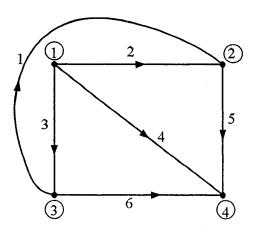

The tree of a graph is one of the most important concepts in graph theory applied to circuit analysis [22]. This concept provides a convenient solution to the problem in a large network. Before introducing the concept, I will review several definitions in graph theory [22].

**Graph**: A graph  $\Gamma$  is a set of branches  $B_r = \{B_{r1}, \dots, B_{r2}\}$  together with a set of nodes  $\{v_1, \dots, v_n\}$  such that every branch in  $B_r$  is incident with two nodes in N.

**Subgraph**:  $\Gamma_1 = (B_{r_1}, N_1)$  is a subgraph of  $\Gamma = (B_r, N)$  if  $\Gamma_1$  is a graph,  $B_{r_1}$  is a subset of  $B_r$  and  $N_1$  is a subset of N.

Connected graph: A connected graph is said to be connected when there is at least one path between every pairs of nodes.

Cut set: Given a connected graph  $\Gamma$ , a cut set X is a set of branches  $\{b_{r_1},...,b_{r_c}\}$  in  $\Gamma$  such that:

- The removal of all braches in X results in a graph that is not connected;

- The removal of all but one branch in X leaves the graph connected.

**Loop**: Let  $\Gamma$  be a connected graph. A loop  $\Lambda$  is a connected subgraph of  $\Gamma$  in which precisely two branches are incident with each node.

Kirchhoff's Voltage Law (KVL) and Kirchhoff's Current Law (KCL) are based on loops and cut sets respectively. To make those definitions clear, an example is presented. Fig. 2.9 shows a connected graph with 4 nodes and 6 braches. The following cut sets are identified in the graph:

$$X_1 = \{2,3,4\}$$

$$X_2 = \{1,2,5\}$$

$$X_3 = \{1,3,6\}$$

$$X_4 = \{4,5,6\}$$

$$X_5 = \{1,2,4,6\}$$

$$X_6 = \{1,3,4,5\}$$

$$X_7 = \{2,3,5,6\}$$

Figure 2.9: A connected graph

If all KCL equations based on cut sets for the graph of Fig. 2.9 are expressed in matrix form, the result is

$$\begin{bmatrix} 0 & 1 & 1 & 1 & 0 & 0 \\ -1 & -1 & 0 & 0 & 1 & 0 \\ 1 & 0 & -1 & 0 & 0 & 1 \\ 0 & 0 & 0 & -1 & -1 & -1 \\ 1 & 1 & 0 & 1 & 0 & 1 \\ 1 & 0 & -1 & -1 & -1 & 0 \\ 0 & 1 & 1 & 0 & -1 & -1 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \\ I_4 \\ I_5 \\ I_6 \end{bmatrix} = \vec{0}$$

(2.19)

or

$$Q_a \vec{I} = \vec{0} \tag{2.20}$$

where  $Q_a$  is the full cut-set matrix. In fact, there are always only n-1 linearly independent rows that can be selected in  $Q_a$ , where n is the number of nodes in the

graph. Therefore the maximum number of linearly independent rows that can be selected in (2.19) is three.

The loops in the graph of Fig. 2.9 are composed of the following branches:

$$\Lambda_{1}: \{1,2,3\}$$

$$\Lambda_{2}: \{1,5,6\}$$

$$\Lambda_{3}: \{1,2,4,6\}$$

$$\Lambda_{4}: \{1,3,4,5\}$$

$$\Lambda_{5}: \{2,3,5,6\}$$

$$\Lambda_{6}: \{2,4,5\}$$

$$\Lambda_{7}: \{3,4,6\}$$

All loop-based KVL equations for the graph of Fig. 2.9 can be grouped in matrix form as

$$\begin{bmatrix} 1 & -1 & 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & -1 \\ 1 & -1 & 0 & 1 & 0 & -1 \\ 1 & 0 & 1 & -1 & 1 & 0 \\ 0 & 1 & -1 & 0 & 1 & -1 \\ 0 & 1 & 0 & -1 & 1 & 0 \\ 0 & 0 & 1 & -1 & 0 & 1 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \\ V_5 \\ V_6 \end{bmatrix} = \vec{0}$$

(2.21)

or

$$B_a \vec{V} = \vec{0} \tag{2.22}$$

where  $B_a$  is the full loop matrix. There are only  $\ell = b - (n-1)$  linearly independent rows in  $B_a$  for a graph with n nodes and b branches. Therefore the maximum number of linearly independent rows in (2.21) is three.

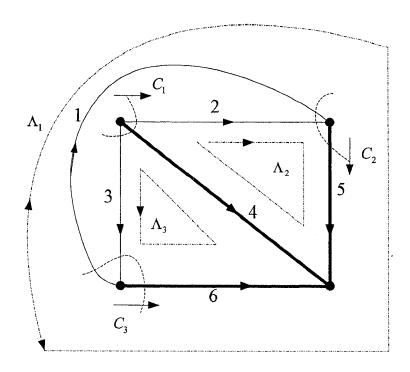

The key issue is the selection of cut sets and loops that result in linearly independent rows of  $Q_a$  and  $B_a$  respectively. The tree of a graph provides the solution to the problems of determining a linearly independent cut set-based KCL equations and loop-based KVL equations. These equations are provided by the unique groups of cut sets and loops that are always associated with a tree.

The theory of the concept, the tree of a graph, is first reviewed.

**Tree**: Let  $\Gamma$  be a connected graph. A tree  $T_r$  is subgraph of  $\Gamma$  such that:

- $\bullet$   $T_r$  is connected

- $T_r$  contains all node of  $\Gamma$

- $\bullet$  T, has no loops

The branches of a connected graph are divided in two groups: those branches that belong to the tree, called tree branches, and those that are not in the tree, called links. The main results that relate trees with cut sets and loops are grouped in the following theorem [23].

Fundamental theorem of graphs: Let  $\Gamma$  be a connected graph with n nodes and b branches and  $T_r$  a tree of  $\Gamma$ . Then:

- There is a unique path along the tree between any pair of nodes;

- There are n-1 tree branches and  $\ell = b (n-1)$  links;

- $\bullet$  Every tree branch of  $T_r$  together with some links defines a unique cut set;

- Every link of  $T_r$  and the unique path on the tree between its two nodes defines a unique loop.

The orientation for cut sets is defined by the associated tree branch. Fig. 2.10 is a graph used to illustrate the use of trees to obtain KCL and KVL equations. The tree branches are indicated by thicker lines. The cut sets associated with tree branches and loops associated with links are indicated in this graph. According to the theorem, there will be n-1=3 tree branches and  $\ell=b-(n-1)=3$  links.

KCL equations for the three cut sets in Fig. 2.10 are written as

$$C_1: I_2 + I_3 + I_4 = 0$$

$C_2: -I_1 - I_2 + I_5 = 0$

$C_3: I_1 - I_3 + I_6 = 0$

or, in matrix form

$$\begin{bmatrix} 0 & 1 & 1 & 1 & 0 & 0 \\ -1 & -1 & 0 & 0 & 1 & 0 \\ 1 & 0 & -1 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \\ I_4 \\ I_5 \\ I_6 \end{bmatrix} = \vec{0}$$

Figure 2.10: Graph used to illustrate the use of trees to obtain KCL and KVL equations.

The orientation for loops is defined by the associated link. The KVL equations derived from the loops are

$$\Lambda_1: V_1 + V_5 - V_6 = 0$$

$$\Lambda_2: V_2 - V_4 + V_5 = 0$$

$$\Lambda_3: V_3 - V_4 + V_6 = 0$$

or, in matrix form,

$$\begin{bmatrix} 1 & 0 & 0 & 0 & 1 & -1 \\ 0 & 1 & 0 & -1 & 1 & 0 \\ 0 & 0 & 1 & -1 & 0 & 1 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \\ V_5 \\ V_6 \end{bmatrix} = \vec{0}$$

### 2.6 Nonlinear Elements in Wave Digital Filters

Modeling nonlinear elements in the wave domain is possible in many cases where the nonlinear element is memoryless [8], in which case its nonlinear characteristic can be mapped directly into the wave domain through the affine transformation that defines the wave variables as a function of the Kirchhoff variables. Nonlinear elements with memory are described by a differential equation rather than an algebraic one. In order to model nonlinear elements with memory, classical WDF principles are no longer adequate. Based on the classical WDF theory, a new class of wave variables and generalized adaptors are used to model a variety of nonlinear elements with memory in the wave domain [9].

#### 2.6.1 Nonlinear Resistors

Under mild conditions we can simulate the behavior of a circuit containing a nonlinear resistor by connecting an appropriate instantaneous map with a reflection-free port of an adaptor [8].

A nonlinear resistor is generally defined as an algebraic relationship of the form F(v,i)=0 in the Kirchhoff variables. The Kirchhoff characteristic of the resistor can be transformed into a wave characteristic of the form f(a,b)=0 through the following mapping:

$$f(a,b) = F(\frac{a+b}{2}, \frac{a-b}{2R}) = 0$$

(2.23)

The conditions that allow us to write the reflected wave b as an explicit function

$b = \widetilde{f}(a)$  of the incident wave a are provided by the implicit function theorem.

In fact, if the characteristic function of the resistor f(a,b) with its derivatives are continuous and if the point  $(a_0,b_0)$  lies on the characteristic of the resistor, then the condition

$$\left. \frac{\partial f}{\partial b} \right|_{(a_0, b_0)} \neq 0 \tag{2.24}$$

guarantees the existence of a function  $\widetilde{f}(\cdot)$  such that  $f(a,\widetilde{f}(a))=0$  in a neighborhood of  $a_0$ .

The nonlinear characteristic F(v,i) = v - v(i) = 0 of a current-controlled nonlinear resistor is mapped onto the wave characteristic

$$f(a,b) = \frac{a+b}{2} - v\left(\frac{a-b}{2R}\right) = 0$$

To check if it guarantees the existence of a function  $\widetilde{f}(\bullet)$ ,

$$\frac{\partial f}{\partial b} = \frac{\partial}{\partial b} \left\{ \frac{a+b}{2} - v \left( \frac{a-b}{2R} \right) \right\}$$

$$= \frac{1}{2} - \frac{\partial v}{\partial i} \frac{\partial i}{\partial b} = \frac{1}{2} + \frac{1}{2R} v' \left( \frac{a-b}{2R} \right)$$

$$v'(i) = \frac{dv}{di}$$

As a result, the local invertibility of the characteristic v=v(i), i.e., the possibility of rewriting it in the form  $b=\widetilde{f}(a)$ , is guaranteed by the condition  $v'(i)\neq -R$ . The same procedure can also be applied to a voltage-controlled resistor with characteristic F(v,i)=i-i(v)=0. The local invertibility condition is given by  $i'(v)\neq -1/R$ .

## 2.6.2 Nonlinear Elements with Memory

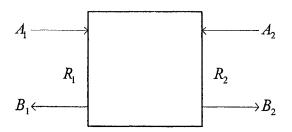

Figure 2.11: Scattering junction

Fig. 2.11 shows a scattering junction of two-port element which can transform the wave pair  $(A_1,B_1)$ , which is referred to the reference transfer function (RTF)  $R_1(z)$ , into the wave pair  $(A_2,B_2)$ , which is referred to  $R_2(z)$ .  $R_1(z)$  and  $R_2(z)$  are the Z transformation of arbitray port "impedance"  $R_1(s)$  and  $R_2(s)$ . Let

$$\begin{split} A_1(z) &= V_1(z) + R_1(z)I_1(z) \\ B_1(z) &= V_1(z) - R_1(z)I_1(z) \\ A_2(z) &= V_2(z) + R_2(z)I_2(z) \\ B_2(z) &= V_2(z) - R_2(z)I_2(z) \end{split}$$

Where  $A_1(z)$  and  $A_2(z)$  are the waves that enter the junction, and  $B_1(z)$  and  $B_2(z)$  are the corresponding reflected waves. The scattering junction is then characterized by the continuity constraints  $V_1(z) = V_2(z)$  and  $I_1(z) + I_2(z) = 0$ .

$$I_{1}(z) = -I_{2}(z) = \frac{A_{1}(z) - A_{2}(z)}{R_{1}(z) + R_{2}(z)}$$

$$B_{1}(z) - A_{2}(z)$$

$$B_{2}(z) - A_{1}(z)$$

$$B_{2}(z) = (1 + K(z))A_{1}(z) - K(z)A_{2}(z)$$

$$B_{2}(z) = (1 + K(z))A_{1}(z) - K(z)A_{2}(z)$$

$$(2.25)$$

where

$$K(z) = \frac{R_2(z) - R_1(z)}{R_2(z) + R_1(z)}$$

(2.26)

The transfer function K(z) characterizes the scattering junction with memory, which

is expected to be causal and stable.

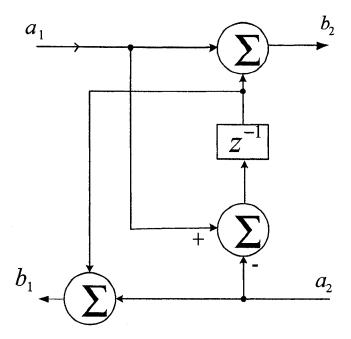

Figure 2.12: (a) Direct implementation of the scattering junction (b) the simplified mode

A direct implementation of equations (2.25) is shown in Fig. 2.12 (a), which can be simplified as shown in Fig. 2.12 (b). From Fig. 2.12, we notice that the wave  $a_1$  that enters port 1 is partially reflected through the transfer function K(z) and partially transmitted to port 2 through 1+K(z), whereas the wave  $a_2$  entering port 2 is partially reflected through -K(z) and partially transmitted through 1-K(z).

When considering the digital implementation of a scattering junction, it is of crucial importance to derive the conditions under which any of its ports do not exhibit any instantaneous reflection, as its interconnection with other circuit ports might give rise to delay free loops. In order to avoid instantaneous reflection of the waves entering the two ports of a digital scattering junction, it is necessary and sufficient for K(z) to exhibit no instantaneous input/output connection, i.e.,  $K(z) = z^{-1} \hat{K}(z)$ , with  $\hat{K}(z)$  causal and stable.

A particular case of wave scattering junctions with memory is represented by the wave digital mutators [11], which are intimately related to a class of two-port analog

elements [10] called mutators, which are built using only operational amplifiers and linear passive resistors and capacitors. Mutators can be used to transform a nonlinear capacitor into a nonlinear resistor while preserving the nonlinear characteristic in the transformed Kirchoff domain. This property can be quite useful as, for example, synthesizing a nonlinear capacitor with prescribed v-q characteristic is much more difficult than implementing a nonlinear resistor with the same characteristic in the v-i plane.

The scattering junction with memory represents a direct extension of the concept of mutator because it is suitable for modeling a wide class of dynamic nonlinear elements.

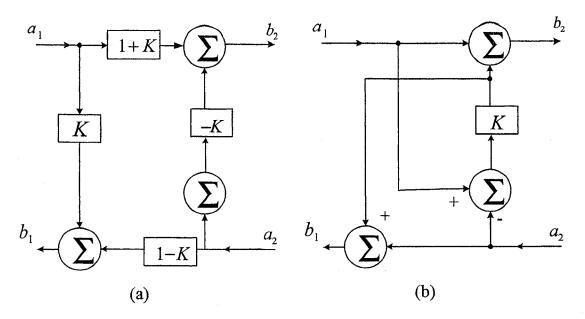

The wave R-C mutator is simply a scattering junction between a capacitive RTF and resistive one. With reference to the equation K(z), the situation can be dealt with by letting  $R_1(s) = R$  and  $R_2(s) = 1/sC$ , C > 0. By applying bilinear transformation, the transfer function K(z) becomes

$$K(z) = \frac{R_2(z) - R}{R_2(z) + R} \qquad R_2(z) = \frac{T}{2C} \frac{1 + z^{-1}}{1 - z^{-1}}$$

Let R = T/2C to eliminate the instantaneous reflections at both ports. In this case, we have  $K(z) = z^{-1}$ .

In order to adapt a capacitive RTF to a resistive one, we can use a scattering junction whose reflection coefficient is replaced by a pure delay and whose second port is left unconnected. As a consequence, the whole scattering junction may be replaced with just one delay element, which is how the classical WDF theory deals with linear capacitors. The following figure shows the structure of R-C mutator.

Figure 2.13: Structure of the R-C mutator

The wave R-C mutator can be used to extend the results on nonlinear resistors to the case of nonlinear capacitors. In fact, the waves at port 2 of the R-C mutator are

$$A_{2}(z) = V(z) + \frac{T}{2C} \frac{1+z^{-1}}{1-z^{-1}} I(z) = V(z) + \frac{1}{C} Q(z)$$

$$B_{2}(z) = V(z) - \frac{T}{2C} \frac{1+z^{-1}}{1-z^{-1}} I(z) = V(z) - \frac{1}{C} Q(z)$$

(2.27)

where Q(z) is associated with the electrical charge q(t),  $\dot{q}(t)=i(t)$ . A nonlinear capacitor can be described by an algebraic relationship of the form P(v,q)=0 between the electrical charge q and the voltage v. C plays the role of reference capacitance in the linear transformation that maps the Kirchhoff characteristic of the nonlinear capacitor onto the wave domain. In order to implement the nonlinear capacitor in the wave domain, we only need to implement a nonlinear map of the form  $b=\widetilde{f}(a)$  and connect it with the capacitive port of the R-C mutator by letting  $a=b_2$  and  $a_2=b$ .

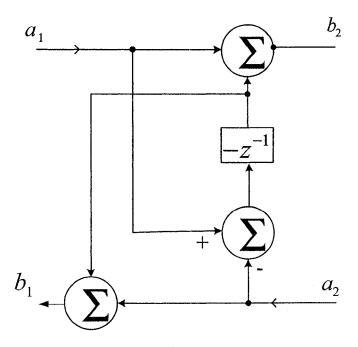

The wave R-L mutator is simply a scattering junction between an inductive RTF and a resistive one. With reference to the equation K(z), let  $R_1(s) = R$  and

$R_2(s) = sL$ , L > 0. After bilinear transformation, the transfer function becomes

$$K(z) = \frac{R_2(z) - R}{R_2(z) + R} \qquad R_2(z) = \frac{2L}{T} \frac{1 + z^{-1}}{1 - z^{-1}}$$

We may eliminate the instantaneous reflection at both ports by letting R = 2L/T, in which case we have  $K(z) = -z^{-1}$ . This is expected from the classical WDF theory. The corresponding R-L mutator results as being a dynamic scattering junction, whose transfer function is just a delay element with sign change. The R-L mutator is shown in Fig. 2.14.

The R-L mutator can be employed for implementing nonlinear inductors of the form M(v, j) = 0. The waves at port 2 of the R-L mutator are

$$A_{2}(z) = V(z) + \frac{2L}{T} \frac{1 - z^{-1}}{1 + z^{-1}} I(z) = V(z) + LJ(z)$$

$$B_{2}(z) = V(z) - \frac{2L}{T} \frac{1 - z^{-1}}{1 + z^{-1}} I(z) = V(z) - LJ(z)$$

(2.28)

where J(z) is the Z-transform of the discretized version of j(t) = di(t)/dt, and L is a constant parameter that plays the role of a reference inductance.

Figure 2.14: Structure of the R-L mutator

### 2.6.3 Circuits with More Than One Nonlinearity

Most of methods concerning nonlinear networks can only work for the circuits that contain a single nonlinearity. In [24], the author proposed a method based on the usage of a vector approach. Any arbitrary number of nonlinearities can be modeled by one single vector-nonlinearity, so that the complete network is the combination of one nonlinear vector-WDF with a delay free feedback, adapted to the linear part of the network which includes a delay. This method is implemented by using the look-up-tables of the nonlinearities. But this method is not useful for networks that contain many nonlinearities since the size of the vector-nonlinearity table will grow exponentially when more nonlinearities are added to the network.

In [25], Felderhoff proposed a convergent relaxation method that can be used to systematically generate a massive parallel algorithm, and simulate the networks with many nonlinear devices. But so far it was only applied for the simulation of a nonlinear transmission line.

Fiedler and Grotstlen [7] proposed a method to treat some special types of nonlinearities in WDF, but this can not be used for nonlinear circuits in general.

# Chapter 3

# LC VCO Design

### 3.1 Introduction

VCOs are widely used in wireless and optical communication systems. In wireless transmission systems, the VCO is used for the frequency synthesizer to generate the local oscillating signal for the modulation and demodulation of the RF signal. In digital optical transmission systems, VCOs are used as the core circuit of the clock recovery circuit, whose output signal is used for data decision and regeneration.

A general VCO can be treated as a black box with an input  $V_{tune}$  and a periodic oscillating output  $V_{out}(t)$ . The VCO is connected to the power supply through  $V_{ss}$  and  $V_{dd}$  [12]. The output voltage  $(V_{out}(t), differential or single ended), is periodic:$

$$V_{out}(t) = V_0 \sin(\omega_c t + \varphi) \tag{3.1}$$

where  $\varphi$  is the phase and  $V_0$  the amplitude. The angular carrier frequency,

$$\omega_c(V_{tune}) = 2\pi f_c(V_{tune}) \tag{3.2}$$

is dependent on the tuning voltage input  $(V_{tune})$ .

We will first review two types of oscillator: ring oscillators and LC oscillators. Secondly an LC VCO is designed. The detailed design process along with simulation results is presented. At last, the layout of the LC VCO is described.

# 3.2 Ring Oscillators and LC Oscillators

According to the structure, the VCO can be divided into two types: ring oscillators and LC Oscillators.

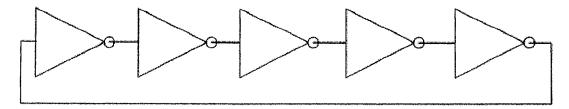

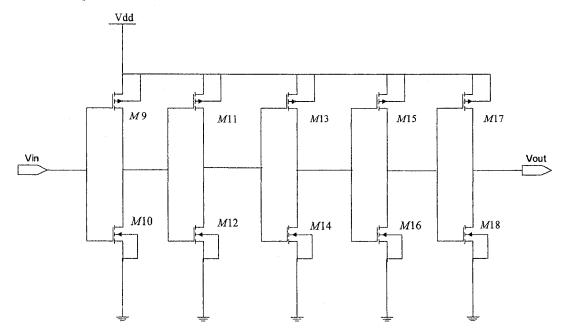

Figure 3.1: Ring oscillator topology

A classical ring oscillator circuit is the connection of amplifiers or inverters in a ring structure. If the phase shift over the ring at one frequency is 360°, the ring will oscillate at that frequency. Fig. 3.1 shows an exemplary ring oscillator topology. Ring oscillators have a very small area and are easy to integrate and design. They feature wide tuning ranges. Their main disadvantage is phase noise.

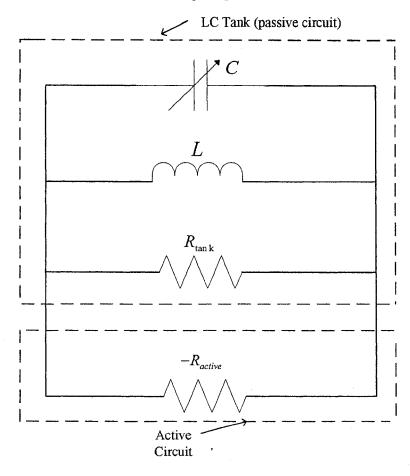

Figure 3.2: Basic LC VCO

The LC VCO consists of an inductor L and a variable capacitor C, building a parallel resonance tank, and an active element -R, compensating the losses of the

resonance tank, which are losses of inductor and the losses of the capacitor. The basic LC oscillator circuit is shown in Fig. 3.2. The circuit results in an oscillator with angular center frequency.

$$\omega_c = \frac{1}{\sqrt{LC}} \tag{3.3}$$

If the capacitance C is proportional to the tuning voltage  $V_{tune}$ ,  $\omega_c$  is dependent on  $V_{tune}$ . The capacitor C not only consists of a variable capacitor to tune the oscillator, it also includes the parasitic or fixed capacitances of the inductor, the active elements, and of any load connected to the VCO. The advantages of LC VCOs are their outstanding phase noise and jitter performance at high frequency. Their main disadvantages are high power consumption and large area.

## 3.3 LC VCO Design

An LC VCO circuit is designed as a case study for WDF simulation. The design uses TSMC CMOS 0.18 µm technology available through CMC Microsystems. The supply voltage is 1.8 V. The design goal is to tune the frequency from 2.5 GHz to 3.0 GHz. The reason for this tuning range is to achieve the highest frequency possible with the 24-pin package which has the limitation of 3 GHz. The following Cadence tools will be used in this design:

- Virtuoso Composer for schematic design

- Analog Environment (Spectre) for schematic simulation and post-layout simulation

- Virtuoso Layout for layout

- Diva for DRC (design rule checking), extraction and LVS (layout vs. schematic)

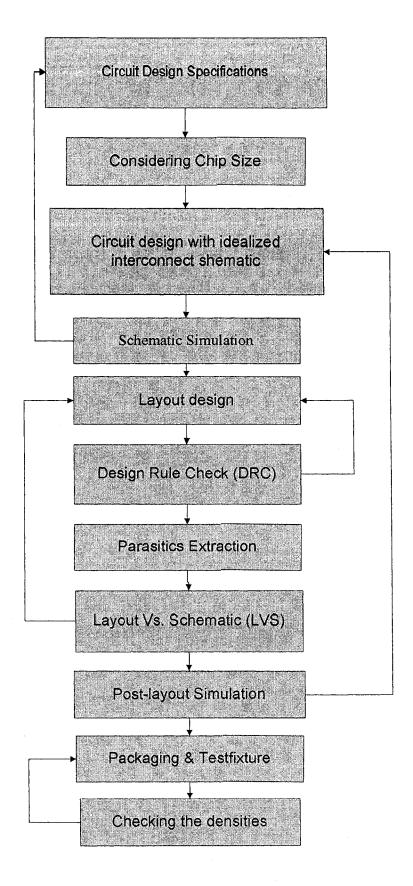

There are many things which need to be considered in the design procedure. Fig. 3.3 shows the flow chart for designs by Cadence tools to make the whole design procedure more understandable.

Figure 3.3: The flow chart for designs by Cadence tools.

## 3.3.1 LC VCO Topology

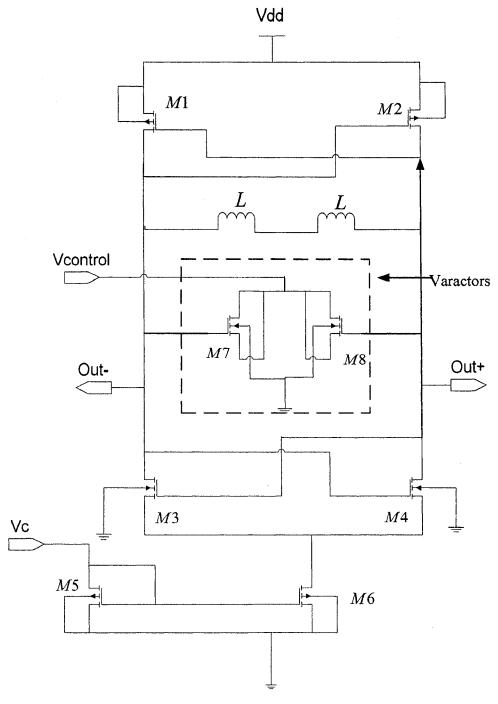

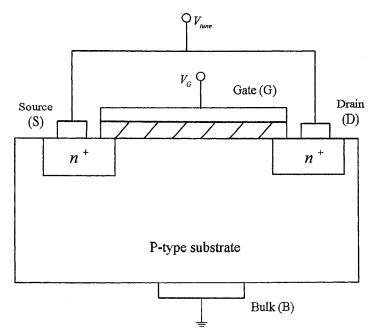

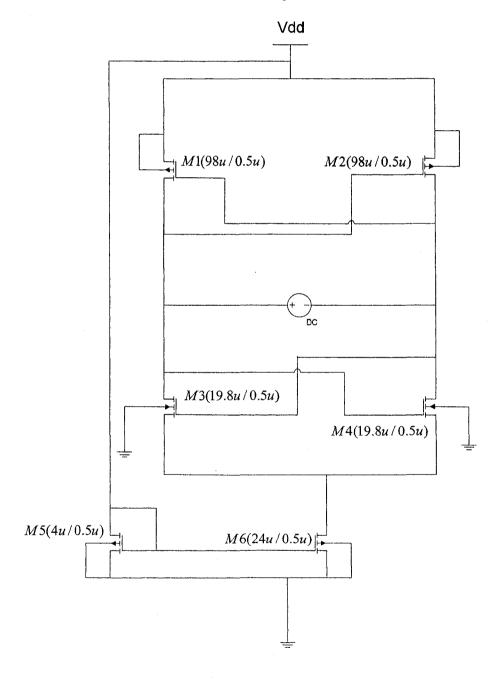

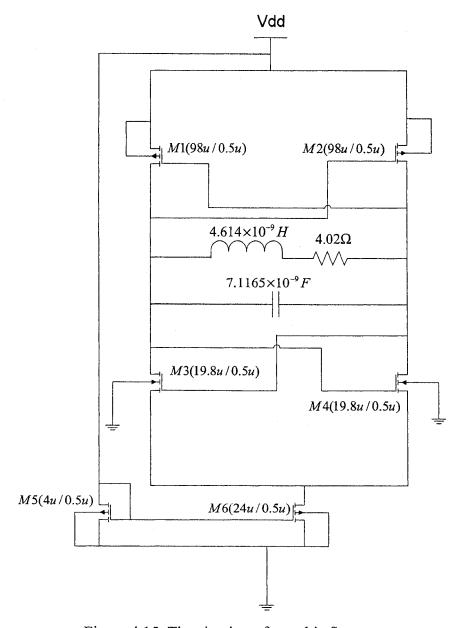

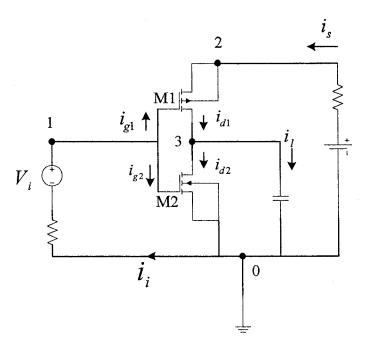

Figure 3.4: LC VCO Schematic (  $Vc=V_{dd}$  )

Many circuits can provide the negative resistance of Fig. 3.2 to compensate for the tank losses. A standard approach for differential VCOs is the use of cross-coupled transistors to generate a negative resistance. The negative resistance should be large enough to overcome the equivalent parallel resistance of the VCO tank circuit to generate the desired oscillation. The complementary cross-coupled oscillator circuit is

the result of using both PMOS and NMOS cross coupled pairs in parallel to generate the negative resistance. Figure 3.4 shows the schematic view of the designed complementary cross-coupled LC VCO. Since the same bias current flows through both the PMOS and NMOS pairs, the negative resistance can be twice as large for the same power. In the complementary circuit, the amplitude is limited by both supply voltage and tail current source. The differential voltage swing is limited to the supply voltage.

In Fig. 3.4, the transistors M5 and M6 compose the current mirror to provide the tail current. The PMOS pair (M1, M2) and NMOS pair (M3, M4) form the negative resistance compensating the VCO losses. Two spiral inductors L have the same values. NMOS transistors M7 and M8 are the NMOS varactors.

The design variables obviously are the inductor parameters, the total tank capacitance C, the width and the length of the transistors and the bias current. Since the interdependences of the design parameters are very complex, it is hard to calculate all parameters according to the equations. Fine tuning is necessary according to simulation results of the DC operating point in the Spectre. The LC VCO design follows the steps shown below,

- Design the spiral inductor

- Design NMOS and PMOS transistors according to the model of Spiral inductor

- Design varactor according to the oscillating frequency range and the parasitic capacitances

- Design the current mirror that can provide enough tail current

#### 3.3.2 Spiral Inductor

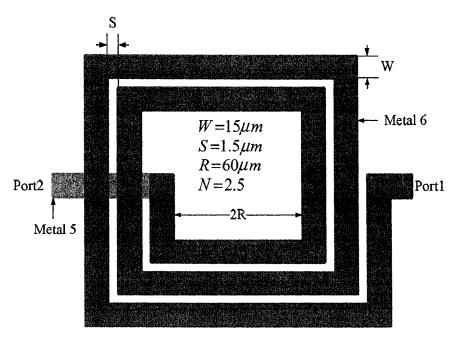

An on-chip planar spiral inductor can be made with many different layout structures. In this design, a square-shaped spiral inductor is employed. This is shown in Fig. 3.5. Any device below the inductor is forbidden due to the magnetic flux that penetrates into the silicon substrate. This flux would affect the device behavior when the device is under spiral inductor. Increasing the turns of spiral inductor will increase the inductance value. In Fig. 3.5, the key parameters of the spiral inductor layout are

### depicted:

- N: number of coil turns

- W: metal width of top metal

- S: metal space of top metal

- R: radius inside inner coil

Figure 3.5: Square spiral inductor layout

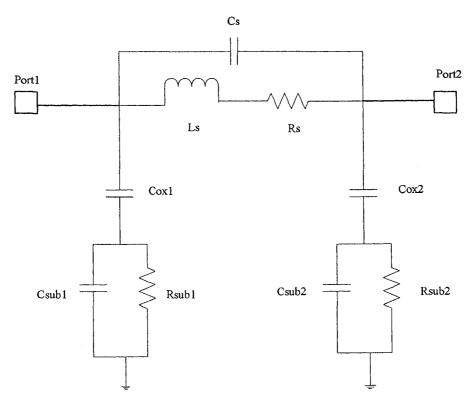

A two-port  $\pi$ -type circuit used to model the spiral inductor is shown in Fig. 3.6. The following is a short explanation of the various components found in the equivalent circuit model [12]:

- $L_s$ : caused by the magnetic flux density of the electromagnetic field

- $R_{sub}$ : is used to model the ohmic losses in the silicon substrate

- $R_s$ : characterizes series resistance of the metal traces.

- ullet  $C_s$ : overlap capacitance between the spiral and the center tap underpass

- $C_{ox}$ : The oxide capacitance between the spiral and substrate

- $C_{sub}$ : is used to characterize the capacitance in substrate.

The expressions that calculate the lumped elements in Fig. 3.6 vary considerably from one model to the other. In [13, 14], they give expressions of L, Rs, Cs, Cox, Rsub, Csub are given as functions of the inductor's geometry. These expressions can be used to approximate the values of those parameters.

For convenience and accuracy, the expressions of those parameters are adopted directly from [15]. Since these expressions are measured and tested by TSMC, they provide a more accurate approximation. The values of these parameters for N=2.5 are shown in Table 3.1 with  $W = 15\mu m$ ,  $S = 1.5\mu m$  and  $R = 60\mu m$ .

| $L_s$   | $R_s$ | $C_s$           | $C_{ox1}$ | $C_{ox2}$ | $C_{sub1}/C_{sub2}$ | $R_{sub1}/R_{sub2}$ |

|---------|-------|-----------------|-----------|-----------|---------------------|---------------------|

| 2.307nH | 2.01Ω | 18.68 <i>fF</i> | 63.99 fF  | 54.5 fF   | 37.63 <i>fF</i>     | 444Ω                |

Table 3.1: The values of spiral inductor parameters

Figure 3.6: Spiral inductor equivalent circuit model

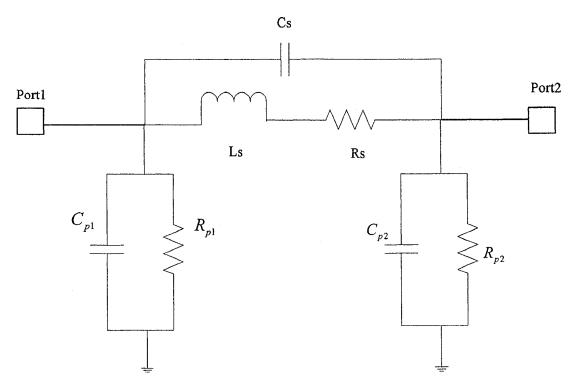

The energy storage and loss mechanisms in an inductor on silicon,  $L_s$ ,  $R_s$ ,  $R_{p(1 \text{ and } 2)}$  and  $C_L = C_{p(1 \text{ and } 2)} + C_s$ , represent the overall inductance, conductor loss, substrate loss, and overall capacitance respectively in Fig. 3.7. The parameters in

Figure 3.7 will be used to calculate the conductance and parasitic capacitance in the tank model. Note that  $R_{p(1 \text{ and } 2)}$  and  $C_{p(1 \text{ and } 2)}$  represent the combined effects of  $C_{ox(1 \text{ and } 2)}$ ,  $C_{sub(1 \text{ and } 2)}$  and  $R_{sub(1 \text{ and } 2)}$ , and hence are frequency dependent [16, 17]. The equations are as follows,

$$R_{p(1 \text{ or } 2)} = \frac{1}{\omega^2 \cdot C_{ox(1 \text{ or } 2)}^2 \cdot R_{sub(1 \text{ or } 2)}} + \frac{R_{sub(1 \text{ or } 2)}(C_{ox(1 \text{ or } 2)} + C_{sub(1 \text{ or } 2)})^2}{C_{ox(1 \text{ or } 2)}^2}$$

(3.4)

$$C_{p(1 \text{ or } 2)} = C_{ox(1 \text{ or } 2)} \cdot \frac{1 + \omega^2 (C_{ox(1 \text{ or } 2)} + C_{sub(1 \text{ or } 2)}) C_{sub(1 \text{ or } 2)} \cdot R_{sub(1 \text{ or } 2)}^2}{1 + \omega^2 (C_{ox(1 \text{ or } 2)} + C_{sub(1 \text{ or } 2)})^2 \cdot R_{sub(1 \text{ or } 2)}^2}$$

(3.5)

Since the values of  $C_{ox1}$  and  $C_{ox2}$  are slightly different, we can assume the following equations for calculation purpose,

$$C_p = C_{p1} \cong C_{p2}$$

$$R_p = R_{p1} \cong R_{p2}$$

(3.6)

Figure 3.7: Simplified spiral inductor equivalent circuit model

#### 3.3.3 NMOS Varactors

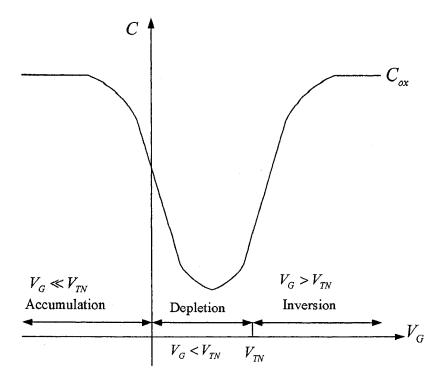

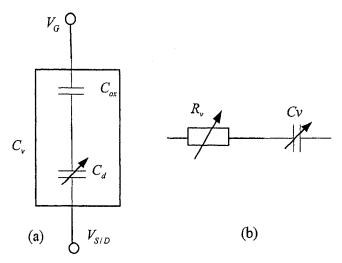

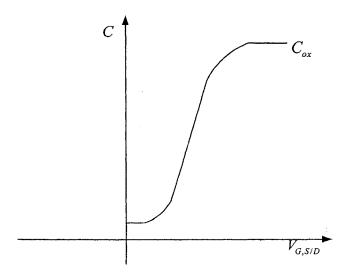

Figure 3.8: Capacitance NMOS structure with gate voltage ( $V_G$ )

NMOS varactors are variable, voltage-controlled capacitors based on the NMOS structure. Figure 3.8 depicts the variation of the capacitance of the NMOS structure with gate voltage. At voltages well below the threshold voltage  $V_{TN}$ , the surface is in accumulation and the capacitance is high and determined by the oxide thickness. As the gate voltage increases, the surface depletion layer forms. In this region, the effective separation of the capacitor plates increases, and the capacitance decrease steadily. The inversion layer forms at the surface as  $V_G$  exceeds the threshold voltage, and the capacitance rapidly increases back to the value determined by the oxide layer thickness.

Figure 3.9 shows a cross-section of an inversion mode NMOS varactor. The NMOS varactor is not a four-terminal device as the transistor but a three-terminal device. The source and drain regions are shorted to apply the voltage  $V_{tune}$  that tunes the variable capacitance. The bulk is grounded and the voltage  $V_G$  is applied to the gate node.

Figure 3.9: Cross section of the inversion mode NMOS varactor  $C_{\rm ox}$  represents the oxide capacitance of the transistor, which is given as

$$C_{ox} = \frac{\mathcal{E}_{ox}}{t_{ox}} W \cdot L \quad , \tag{3.7}$$

with  $t_{ox}$  being the thickness and  $\varepsilon_{ox}$  being the dielectric constant of the oxide.  $C_{ox}$  is directly proportional to the transistor area, expressed through the factors W (width of the NMOS) and L (length of the NMOS). The silicon substrate is connected to the lowest potential to prevent the transistor from entering accumulation region since we need a linear capacitance range. The upper limit of the capacitance is determined by  $C_{ox}$ . The capacitance value changes depending on the voltage across the gate and shorted Drain-Source terminals. Increasing the voltage towards the threshold voltage results in establishing a surface layer between gate and shorted Drain-source. The total capacitance is a combination of a voltage dependent depletion-layer capacitance  $C_d$  in series to the oxide capacitance [12] [18]. This is shown in Fig. 3.10(a).

$$\frac{1}{C_{v}} = \frac{1}{C_{ox}} + \frac{1}{C_{d}} \tag{3.8}$$

The generally assumed model of the NMOS varactor is shown in Fig. 3.10(b) [12].

R, is variable resistance. The relationship between the variable capacitance of the NMOS varactor and the voltage between gate and source/drain terminals is shown in Fig. 3.11.

Figure 3.10: (a)Total capacitance of the NMOS varactor in depletion; (b)the generally assumed model of NMOS varactor.

Figure 3.11: Variable capacitance of the NMOS Varactor

#### 3.3.4 Tank Model Calculation Along with Simulation Results

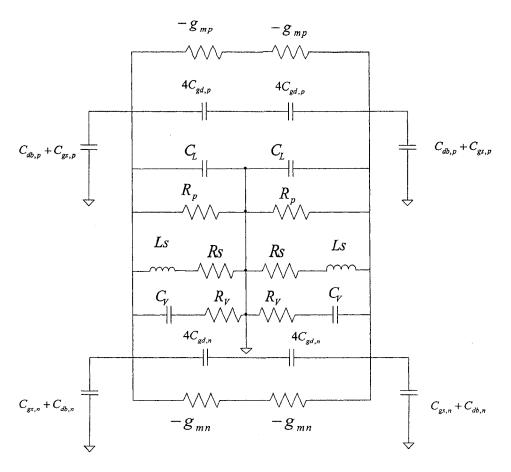

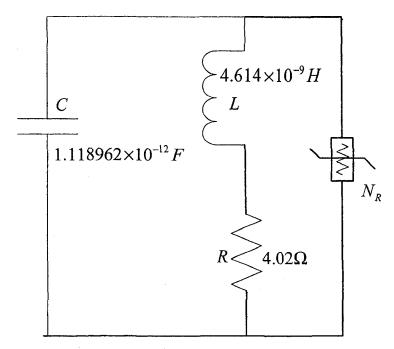

The equivalent circuit model for the complementary cross-coupled LC VCO of Fig. 3.4 is depicted in Fig. 3.12. There are four primary parameters that are closely related to the oscillator behavior and will be helpful in the derivation of the constraints. These parameters are the effective tank conductance  $g_{tank}$ , the effective

negative conductance  $g_{active}$ , the tank capacitance  $C_{tank}$ , and the tank inductance  $L_{tank}$  [19, 20, 21].

Figure 3.12: The tank model of the LC VCO

The equations for those parameters are shown as follows,

$$f = \frac{1}{2\pi\sqrt{L_{\text{tank}}C_{\text{tank}}}} \tag{3.9}$$

$$L_{\text{tank}} = 2Ls \tag{3.10}$$

$$C_{\text{tank}} = \frac{1}{2} \left( 4C_{gd,n} + C_{gs,n} + C_{db,n} + 4C_{gd,p} + C_{gs,p} + C_{db,p} + C_L + C_V \right)$$

(3.11)

$$g_{tank} = \frac{g_{on} + g_{op} + g_{v} + g_{L}}{2} , \qquad (3.12)$$

where  $g_{\nu}$  is the effective parallel varactor conductance and  $g_{L}$  is the effective parallel inductor conductance, which are respectively given by

$$g_{L} = \frac{1}{R_{p}} + \frac{R_{s}}{(L_{s}\omega)^{2}}$$

(3.13)

$$g_{\nu} = (C_{\nu}\omega)^2 \cdot R_{\nu} \tag{3.14}$$

$g_{on}$  is the output conductance of the NMOS transistors and  $g_{op}$  is the output conductance of the PMOS transistors. Usually these two conductances are low enough compared with  $g_L$  to be neglected.

$$g_{active} = \frac{g_{mn} + g_{mp}}{2} \tag{3.15}$$

$$g_{mn} = \frac{\partial I_D}{\partial V_{GS \ VDScont}} = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D} \quad , \tag{3.16}$$

where  $g_{mn}$  and  $g_{mp}$  are the transconductance of the NMOS and PMOS transistors.

$\mu_n$  and  $I_D$  are the hole mobility and drain current respectively.

$$g_{active} \ge K \cdot g_{tank,max}$$

(3.17)

where K usually has a value of 2 to 3 to guarantee reliable start-up.

$$I_{\text{tank.max}} \cong I_{tail} \tag{3.18}$$

$$V_{out+/out-} \cong \frac{I_{tail}}{g_{I}/2} \tag{3.19}$$